- Címlap

- LED kijelzők meghajtása

- Permetező projekt

- PIC18FxxK42

- PIC18FxxK42 I2C regiszterei

- PIC18FxxK42 órajel beállítása

- Pic18FxxK42 regiszterei

- Láb hozzárendelés PIC18FxxK42

- Pic18 I2C programozás

- PIC18FxxK42 I2C kommunikáció

- EEPROM memória használata

- LIN UART-tal fordítás

- LM75A és PIC18F45K42 I2C1 program

- Objektumok

- Pic18FxxK42 konfigurálás

- SPI

- UART PIC18(L)F45K42

- Watchdog Timer

- PIC18F45K42 timer2,-4,-6

- I2C modul 1

- PIC18F45K22 I2C lépései

- PIC18F45K42 USART regiszterei és azok magyarázata II.

- PIC18F45K42 USART regiszterei

- PIC18F45K42 timer1,-3,-5

- UART PIC18F45K42

- PIC18 utasításkészlete

- USART mudullal aszinkron kapcsolat két mikrokontroller közt

- CAN kommunikáció

- DS3231SN RTC

- Dell T 5600

- E-paper

- EGYÉB jegyzet

- ESP 8266 WiFi modul

- ESP-07 ESP-12x

- ESP-12F WiFi modul

- ESP32

- ESP8266

- Egyéb (elektronika)

- Emeléskijelző projekt

- Giroszkóp

- HASZNOSAK

- Hasznos általános linkek

- Illesztő modulok

- Kapcsolások, megoldások

- Kiszajú műveleti erősítő

- Konfigurálás

- LIN kommunikáció UART-tal

- MPASM PIC18

- Nyomásmérés MS5803-05BA-val

- Nyomásmérő I2C

- Nyomásszenzor SPD8xx I2C

- Nyák, nyáktervezés

- Operációs rendszerek

- PIC 18 mikrokontrollerek

- PIC18(L)F47K40

- PIC18(L)F65K40

- PIC18F45(K)50

- PIC18F87k22(80 láb)

- PROGRAMOZÁS

- Programozás

- Python 3

- RAUCH 2057153

- RDS

- RTC TLC 5947-el

- Rádiókapcsolat két mikrokontroller között

- Számítógépes programok

- TCS34725 színérzékelő

- TLC 5947

- TTP223 kapacitív nyomógomb

- USB + USB AN1310-el

- Ulefone Power 2

- Vektoros megszakítások

- Vetőgép

- Webfejlesztés

- WiFi, Bluetooth modulok

- Pickit 3 programozó

- Pic-Ethernet-Pic

- LM75A

- PWM CCPx modullal

- PWM PWMx modullal

- NCO

- TCS 3200 RGB érzékelés

- Nyáktervezés

- Oktatás

- PIC 24 mikrokontrollerek

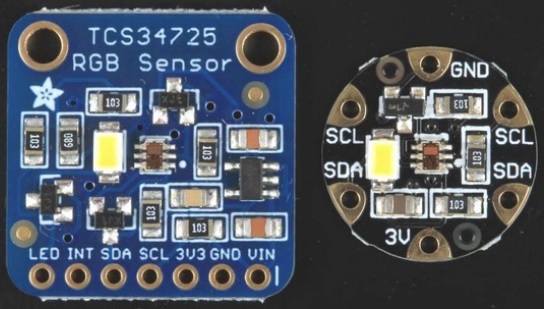

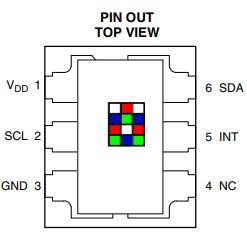

TCS34725 színérzékelő

Adatlap (IC) PDF : Itt!

Modul PDF: Itt!

TCS34725 színérzékelő

Másik típus amivel itt nem foglalkozunk: ISL29125

|

|

Eszközcím = 0x29

| 3. | Regiszterek és használatuk |

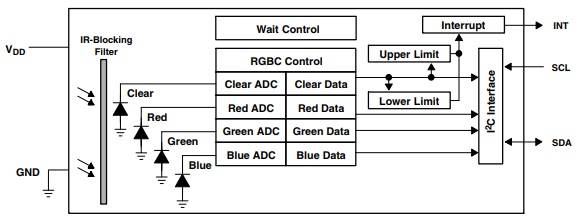

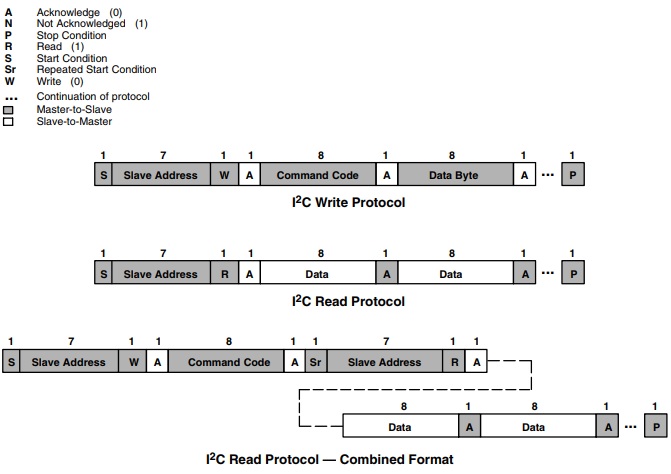

| Beállító regiszter beállítása A TCS3472-t adatrekordok és egy soros interfészen keresztül elérhető parancsregiszter vezérli és felügyeli. Ezek a regiszterek számos vezérlési funkciót biztosítanak, és az ADC-konverziók eredményeinek meghatározásához olvashatók. A regiszterkészletet a 3. táblázat tartalmazza. Adatlap: 13. oldal. Egy adott nyilvántartáshoz való hozzáférés mechanizmusa a használt protokolltól függ. Lásd az I2C fejezetet protokollokat az előző oldalakon. Általában véve először a COMMAND regisztert írja le, hogy megadja a konkrét ellenőrző-állapot-adatregiszter a következő olvasási / írási műveletekhez. Az adatfolyamban a színátalakító címének a <7:1> biteken és a <0> biten az R/!W megadása után kell megadni, hogy a 20 regiszter közül melyikkkel akarunk kommunikálni. Ezt a kiválasztó utasítást nevezzük "Command Code"-nek, regiszterét pedig "COMMAND" regiszternek. A COMMAND regiszternek nincs címe, értelemszerűen az első adatok neki szólnak. |

Register Set The TCS3472 is controlled and monitored by data registers and a command register accessed through the serial interface. These registers provide for a variety of control functions and can be read to determine results of the ADC conversions. The register set is summarized in Table 3. The mechanics of accessing a specific register depends on the specific protocol used. See the section on I2C protocols on the previous pages. In general, the COMMAND register is written first to specify the specific control-status-data register for subsequent read/write operations. |

| CÍM | REGISZTER NEVE | R/W | REGISZTER FUNKCIÓJA | RESET |

| — | COMMAND | W | A regiszter címét adja meg (Specifies register address) |

0x00 |

| 0x00 | ENABLE | R/W | Engedélyezi az állapotokat és a megszakításokat (Enables states and interrupts) |

0x00 |

| 0x01 | ATIME | R/W | RGBC idő (RGBC time) |

0xFF |

| 0x03 | WTIME | R/W | Várakozási idő (Wait time) |

0xFF |

| 0x04 | AILTL | R/W | Fényerősség (fehér szín) megszakítás alacsony küszöb alacsony bájtja (Clear interrupt low threshold low byte) |

0x00 |

| 0x05 | AILTH | R/W | Fényerősség (fehér szín) megszakítás alacsony küszöb magas bájtja (Clear interrupt low threshold high byte) |

0x00 |

| 0x06 | AIHTL | R/W | Fényerősség (fehér szín) megszakítás magas küszöb alacsony bájtja (Clear interrupt high threshold low byte) |

0x00 |

| 0x07 | AIHTH | R/W | Fényerősség (fehér szín) megszakítás magas küszöb magas bájtja (Clear interrupt high threshold high byte) |

0x00 |

| 0x0C | PERS | R/W | Megszakítási érzékenység (hányszor érzékelt eltérést) (Interrupt persistence filter) |

0x00 |

| 0x0D | CONFIG | R/W | Konfiguráció (Configuration) |

0x00 |

| 0x0F | CONTROL | R/W | Ellenőrzés (Contro) |

0x00 |

| 0x12 | ID | R | Eszköz azonosító (Device ID) |

ID |

| 0x13 | STATUS | R | Eszköz állapota (Device status) |

0x00 |

| 0x14 | CDATAL | R | Adatok fehér alacsony bájt (Clear data low byte) |

0x00 |

| 0x15 | CDATAH | R | Adatok nagy bájt törlése (Clear data high byte) |

0x00 |

| 0x16 | RDATAL | R | Piros adat alacsony bájt (Red data low byte) |

0x00 |

| 0x17 | RDATAH | R | Piros adat magas byte (Red data high byte) |

0x00 |

| 0x18 | GDATAL | R | Zöld adatok alacsony byteGreen adatok alacsony byte (Green data low byte) |

0x00 |

| 0x19 | GDATAH | R | Green data high byte (Zöld adat magas byte) |

0x00 |

| 0x1A | BDATAL | R | Blue data low byte (Kék adat alacsony bájt) |

0x00 |

| 0x1B | BDATAH | R | Kék adat magas byte (Blue data high byte) |

0x00 |

| 3.1. | "COMMAND" regiszter |

| Parancsregiszter (Dok.: 14. old.) A parancsregiszter meghatározza a célregiszter címét a jövőbeli írási és olvasási műveletekhez. |

Command Register The command register specifies the address of the target register for future write and read operations. |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | ||

| Command | CMD | TYPE | ADDR/SF | --- | |||||

| MEZŐ FIELD |

BITEK BITS |

LEÍRÁS DESCRIPTION |

|

| CMD | 7 | Válassza ki a parancsregisztert. A COMMAND regiszter címzéséhez 1-et kell írni. Select Command Register. Must write as 1 when addressing COMMAND register. |

|

| TYPE | 6:5 | Kiválasztja a következő adattovábbítás során követendő tranzakció típusát: Selects type of transaction to follow in subsequent data transfers |

|

| FIELD VALUE | INTEGRÁCIÓS IDŐ: INTEGRATION TIME |

||

| 00 | Ismételt bájtprotokoll tranzakció Repeated byte protocol transaction |

||

| 01 | Automatikus növekedésű protokollú tranzakció Auto-increment protocol transaction |

||

| 10 | Fenntartva - Ne használja Reserved — Do not use |

||

| 11 | Speciális funkció - Lásd az alábbi leírást Special function — See description below |

||

| A bájt protokoll ismételten elolvassa ugyanazt a regisztert minden egyes adathozzáférés esetén. A blokk protokoll automatikusan növekszik az egymást követő bájtok olvasásához. Byte protocol will repeatedly read the same register with each data access. Block protocol will provide auto-increment function to read successive bytes. |

|||

| ADDR/SF | 4:0 | Cím mező / speciális funkciómező. A tranzakció típusától függően, lásd fent, ez a mező egy speciális függvényparancsot ad meg, vagy kiválasztja a specifikus vezérlő-állapot-adatregisztert a következő olvasási és írási tranzakciókhoz. Az alább felsorolt mezők értékei csak a speciális funkcióparancsokra vonatkoznak: Address field/special function field. Depending on the transaction type, see above, this field either specifies a special function command or selects the specific control-status-data register for subsequent read and write transactions. The field values listed below only apply to special function commands: |

|

| FIELD VALUE | KAPOTT ÉRTÉK READ VALUE |

||

| 00110 | Fehér (fényerősség) csatorna megszakítás Clear channel interrupt clear |

||

| más other |

Fenntartva - Ne írjon Reserved — Do not write |

||

| A fehér csatorna (fényerősség) megszakítás és függőben levő megszakítás visszaállítása alapállásra. The Clear channel interrupt clear special function clears any pending interrupt and is self-clearing. |

|||

| 3.2. | "Enable" regiszter |

| Enable (engedélyező) regiszter (0x00) (Dok.: 15. old.) Az Enable regiszter elsősorban a TCS3472 készülék be- és kikapcsolására, valamint a funkciók és megszakítások engedélyezésére szolgál az 5. táblázatban látható módon. |

Enable Register (0x00) The Enable register is used primarily to power the TCS3472 device on and off, and enable functions and interrupts as shown in Table 5. |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | ||

| ENGEDÉLYEZÉS ENABLE |

Fenntartott Resetved |

AIEN | WEN | Fenntartott Resetved |

AEN | PON | Address 0x00 |

||

| FIELD | BITS | DESCRIPTION |

| Reserved | 7:5 | Fenntartott. Értéke=0 Reserved. Write as 0. |

| AIEN | 4 | RGBC megszakítás engedélyezése. Megvalósulásához az RGBC megszakítái feltételnek teljesülni kell, vagyis ezzel a bittel (AIEN=1) csak engedélyezzük. RGBC interrupt enable. When asserted, ermits RGBC interrupts to be generated. |

| WEN | 3 | Várakozás engedélyezése. Ez a bit aktiválja a várakozási funkciót. Az 1-re állítása aktiválja a várakozási időt. A 0-ra állítása letiltja a várakozási időt. Wait enable. This bit activates the wait feature. Writing a 1 activates the wait timer. Writing a 0 disables the wait timer. |

| Reserved | 2 | Fenntartott. Értéke=0 Reserved. Write as 0. |

| AEN | 1 | Az RGBC engedélyezése. Ez a bit a kétcsatornás ADC-t aktiválja. Az 1 írása aktiválja az RGBC-t. A 0 írása letiltja az RGBC-t. RGBC enable. This bit actives the two-channel ADC. Writing a 1 activates the RGBC. Writing a 0 disables the RGBC. |

| PON 1, 2 | 0 | Bekapcsolás. Ez a bit aktiválja a belső oszcillátort, hogy lehetővé tegye az időzítők és az ADC (konvertáló) csatornák működését. Az 1 írása aktiválja az oszcillátort. A 0 írása letiltja az oszcillátort. Power ON. This bit activates the internal oscillator to permit the timers and ADC channels to operate. Writing a 1 activates the oscillator. Writing a 0 disables the oscillator. |

Megjegyzés: |

1. További információkért lásd: Energiagazdálkodási szakaszt. / See Power Management section for more information. 2. Az RGBC megkezdése előtt legalább 2,4 ms-os intervallumnak kell eltelnie a PON=1 után. A minimum interval of 2.4 ms must pass after PON is asserted before an RGBC can be initiated. |

| 3. | "COMMAND" regiszter |

"RGBC Timing" regiszter

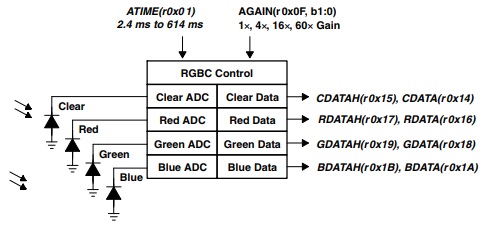

| RGBC időzítőregiszter (0x01) (Dok.: 16. old.) Az RGBC időzítési regisztere szabályozza az RGBC tiszta és IR csatornás ADC-k belső integrációs idejét 2,4 ms-os lépésekben. Max. RGBC-szám = (256 - ATIME) × 1024 maximum 65535-ig. |

RGBC Timing Register (0x01) The RGBC timing register controls the internal integration time of the RGBC clear and IR channel ADCs in 2.4-ms increments. Max RGBC Count = (256 − ATIME) × 1024 up to a maximum of 65535. |

| FIELD | BITS | DESCRIPTION | |||

| ATIME | 7:0 | VALUE | INTEG_CYCLES | TIME | MAX COUNT |

| 0xFF | 1 | 2.4 ms | 1024 | ||

| 0xF6 | 10 | 24 ms | 10240 | ||

| 0xD5 | 42 | 101 ms | 43008 | ||

| 0xC0 | 64 | 154 ms | 65535 | ||

| 0x00 | 256 | 700 ms | 65535 | ||

| 3. | "COMMAND" regiszter |

"Wait Time" regiszter

| Várakozási idő regisztrálása (0x03) (Dok.: 16. old.) A várakozási idő 2,4 ms-os lépésekben van megadva, kivéve, ha a WLONG bit be van állítva, ebben az esetben a várakozási idő 12 × hosszabb. A WTIME-t 2-es kiegészítőként programozzuk. |

Wait Time Register (0x03) Wait time is set 2.4 ms increments unless the WLONG bit is asserted, in which case the wait times are 12× longer. WTIME is programmed as a 2’s complement number. |

| FIELD | BITS | DESCRIPTION | |||

| WTIME | 7:0 | REGISTER VALUE | WAIT TIME | TIME (WLONG = 0) | TIME (WLONG = 1) |

| 0xFF | 1 | 2.4 ms | 0.029 sec | ||

| 0xAB | 85 | 204 ms | 2.45 sec | ||

| 0x00 | 256 | 614 ms | 7.4 sec | ||

| 3. | "COMMAND" regiszter |

"RGBC Interrupt" Threshold regiszter

| RGBC megszakítási küszöbnyilvántartások (0x04 - 0x07) (Dok.: 17. old.) Az RGBC megszakítási küszöbérték-regiszterei megadják azokat az értékeket, amelyeket magas és alacsony triggerpontként használnak a megszakítás generálásához. Ha a tiszta csatorna által generált érték az alsó küszöbérték alatt van, vagy a magasabb küszöbérték felett van, akkor a megszakítócsapra megszakítás történik. |

RGBC Interrupt Threshold Registers (0x04 − 0x07) The RGBC interrupt threshold registers provides the values to be used as the high and low trigger points for the comparison function for interrupt generation. If the value generated by the clear channel crosses below the lower threshold specified, or above the higher threshold, an interrupt is asserted on the interrupt pin. |

| REGISTER | ADDRESS | BITS | DESCRIPTION |

| AILTL | 0x04 | 7:0 | RGBC tiszta csatorna alacsony küszöbérték alacsonyabb bájt RGBC clear channel low threshold lower byte |

| AILTH | 0x05 | 7:0 | RGBC tiszta csatorna alacsony küszöbérték felső bájtja RGBC clear channel low threshold upper byte |

| AIHTL | 0x06 | 7:0 | RGBC tiszta csatorna magas küszöbérték alacsonyabb bájt RGBC clear channel high threshold lower byte |

| AIHTH | 0x07 | 7:0 | RGBC tiszta csatorna magas küszöb felső bájtja RGBC clear channel high threshold upper byte |

| 3.x | Persistence Register regiszter |

| Perzisztencia-nyilvántartás (0x0C) (Dok.: 17. old.) A tartóssági regiszter szabályozza az eszköz szűrési megszakítási képességeit. A konfigurálható szűrés lehetővé teszi, hogy az egyes integrációs ciklusok után megszakítások keletkezzenek, vagy ha az integráció olyan eredményt hozott létre, amely kívül esik a küszöbnyilvántartás által meghatározott időn belül. |

Persistence Register (0x0C) The persistence register controls the filtering interrupt capabilities of the device. Configurable filtering is provided to allow interrupts to be generated after each integration cycle or if the integration has produced a result that is outside of the values specified by the threshold register for some specified amount of time. |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | ||

| PERS | Fenntartott Resetved |

APERS | Address 0x0C |

||||||

| FIELD | BITS | DESCRIPTION | ||

| PPERS | 7:4 | Reserved | ||

| APERS | 3:0 | Interrupt persistence. Controls rate of interrupt to the host processor | ||

| FIELD VALUE | MEANING | INTERRUPT PERSISTENCE FUNCTION | ||

| 0000 | Mindig Every |

Minden RGBC ciklus megszakítást generál Every RGBC cycle generates an interrupt |

||

| 0001 | 1 | 1-szer fehér csatornaérték a küszöb tartományon kívül 1 clear channel value outside of threshold range |

||

| 0010 | 2 | 2-szer fehér csatornaérték a küszöb tartományon kívül 2 clear channel value outside of threshold range |

||

| 0011 | 3 | 3-szor fehér csatornaérték a küszöb tartományon kívül 3 clear channel value outside of threshold range |

||

| 0100 | 6 | 6-szor fehér csatornaérték a küszöb tartományon kívül 6 clear channel value outside of threshold range |

||

| 0101 | 10 | 10-szer fehér csatornaérték a küszöb tartományon kívül 10 clear channel value outside of threshold range |

||

| 0110 | 15 | 15-ször fehér csatornaérték a küszöb tartományon kívül 15 clear channel value outside of threshold range |

||

| 0111 | 20 | 20-szor fehér csatornaérték a küszöb tartományon kívül 20 clear channel value outside of threshold range |

||

| 1000 | 25 | 25-ször fehér csatornaérték a küszöb tartományon kívül 25 clear channel value outside of threshold range |

||

| 1001 | 30 | 30-szor fehér csatornaérték a küszöb tartományon kívül 30 clear channel value outside of threshold range |

||

| 1010 | 35 | 35-ször fehér csatornaérték a küszöb tartományon kívül 35 clear channel value outside of threshold range |

||

| 1011 | 40 | 40-szer fehér csatornaérték a küszöb tartományon kívül 40 clear channel value outside of threshold range |

||

| 1100 | 45 | 45-ször fehér csatornaérték a küszöb tartományon kívül 45 clear channel value outside of threshold range |

||

| 1101 | 50 | 50-szer fehér csatornaérték a küszöb tartományon kívül 50 clear channel value outside of threshold range |

||

| 1110 | 55 | 55-szer fehér csatornaérték a küszöb tartományon kívül 55 clear channel value outside of threshold range |

||

| 1111 | 60 | 60-szor fehér csatornaérték a küszöb tartományon kívül 60 clear channel value outside of threshold range |

||

| 3. | "COMMAND" regiszter |