- Címlap

- LED kijelzők meghajtása

- Permetező projekt

- PIC18FxxK42

- PIC18FxxK42 I2C regiszterei

- PIC18FxxK42 órajel beállítása

- Pic18FxxK42 regiszterei

- Láb hozzárendelés PIC18FxxK42

- Pic18 I2C programozás

- PIC18FxxK42 I2C kommunikáció

- EEPROM memória használata

- LIN UART-tal fordítás

- LM75A és PIC18F45K42 I2C1 program

- Objektumok

- Pic18FxxK42 konfigurálás

- SPI

- UART PIC18(L)F45K42

- Watchdog Timer

- PIC18F45K42 timer2,-4,-6

- I2C modul 1

- PIC18F45K22 I2C lépései

- PIC18F45K42 USART regiszterei és azok magyarázata II.

- PIC18F45K42 USART regiszterei

- PIC18F45K42 timer1,-3,-5

- UART PIC18F45K42

- PIC18 utasításkészlete

- USART mudullal aszinkron kapcsolat két mikrokontroller közt

- CAN kommunikáció

- DS3231SN RTC

- Dell T 5600

- E-paper

- EGYÉB jegyzet

- ESP 8266 WiFi modul

- ESP-07 ESP-12x

- ESP-12F WiFi modul

- ESP32

- ESP8266

- Egyéb (elektronika)

- Emeléskijelző projekt

- Giroszkóp

- HASZNOSAK

- Hasznos általános linkek

- Illesztő modulok

- Kapcsolások, megoldások

- Kiszajú műveleti erősítő

- Konfigurálás

- LIN kommunikáció UART-tal

- MPASM PIC18

- Nyomásmérés MS5803-05BA-val

- Nyomásmérő I2C

- Nyomásszenzor SPD8xx I2C

- Nyák, nyáktervezés

- Operációs rendszerek

- PIC 18 mikrokontrollerek

- PIC18(L)F47K40

- PIC18(L)F65K40

- PIC18F45(K)50

- PIC18F87k22(80 láb)

- PROGRAMOZÁS

- Programozás

- Python 3

- RAUCH 2057153

- RDS

- RTC TLC 5947-el

- Rádiókapcsolat két mikrokontroller között

- Számítógépes programok

- TCS34725 színérzékelő

- TLC 5947

- TTP223 kapacitív nyomógomb

- USB + USB AN1310-el

- Ulefone Power 2

- Vektoros megszakítások

- Vetőgép

- Webfejlesztés

- WiFi, Bluetooth modulok

- Pickit 3 programozó

- Pic-Ethernet-Pic

- LM75A

- PWM CCPx modullal

- PWM PWMx modullal

- NCO

- TCS 3200 RGB érzékelés

- Nyáktervezés

- Oktatás

- PIC 24 mikrokontrollerek

Watchdog Timer

Adatlap (pdf): PIC18F(L)xxK42.pdf

Watchdog Timer D: 178. old.

Watchdog regiszterei a honlapon: Itt!

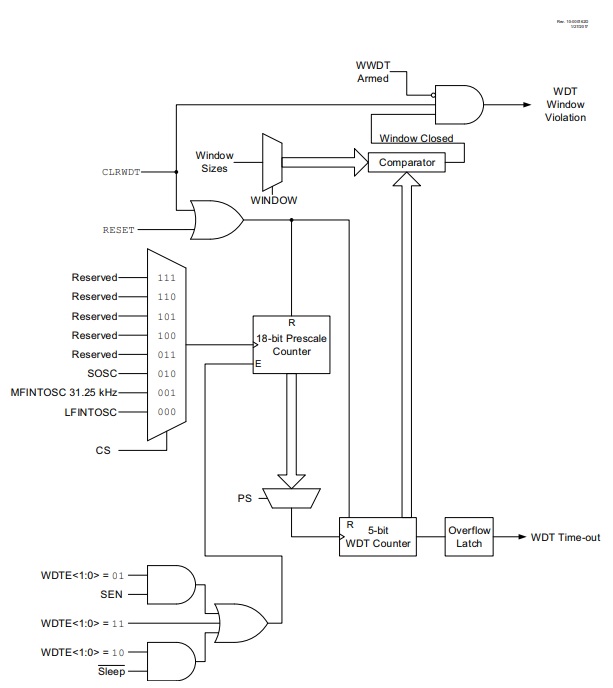

| 1.0 WINDOWED WATCHDOG TIMER (WWDT) A Watchdog időzítő (WDT) olyan rendszer időzítő, amely egy Reset-et generál, ha a firmware nem ad ki CLRWDT utasítást az időkorláton belül. A Watchdog időzítőt általában a rendszer váratlan eseményekből való helyreállítására használják. A Windowed Watchdog Timer (WWDT) különbözik attól, hogy a CLRWDT utasításokat csak akkor fogadják el, ha az adott időn belül egy adott ablakon történik. A WWDT a következő jellemzőkkel rendelkezik: • Választható óraforrás • Több üzemmód - A WWDT mindig be van kapcsolva - A WWDT kikapcsolt állapotban van - A WWDT szoftvert vezérli - A WWDT mindig ki van kapcsolva • A konfigurálható időtúllépés időtartama 1 ms és 256 másodperc között van (névleges) • Konfigurálható ablakméret az időkorlát 12,5% -tól 100% -áig • Többszörös visszaállítási feltételek |

1.0 WINDOWED WATCHDOG TIMER (WWDT) The Watchdog Timer (WDT) is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events. The Windowed Watchdog Timer (WWDT) differs in that CLRWDT instructions are only accepted when they are performed within a specific window during the time-out period. The WWDT has the following features: • Selectable clock source • Multiple operating modes - WWDT is always On - WWDT is off when in Sleep - WWDT is controlled by software - WWDT is always Off • Configurable time-out period is from 1 ms to 256s (nominal) • Configurable window size from 12.5% to 100% of the time-out period • Multiple Reset conditions |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 11.1 Független óraforrás A WWDT időalapját a 31 kHz-es LFINTOSC vagy 31,25 kHz MFINTOSC belső oszcillátorokból nyerheti, a WDTE <1: 0> értékétől függően. Konfigurációs bitek. Ha WDTE = 0b1x, akkor az óraforrás a WDTCCS <2: 0> konfigurációs bitek függvényében engedélyezve lesz. Ha WDTE = 0b01, akkor az SEN bitet a szoftverrel kell beállítani, hogy engedélyezze a WWDT-t, és az óraforrás a CS-bitek által engedélyezve legyen a WDTCON1 regiszterben. Ebben a fejezetben az időintervallumok legalább 1 ms névleges intervallumon alapulnak. Az LFINTOSC és az MFINTOSC tűréshatárokat lásd a 44.0 „Elektromos specifikációk” fejezetben. |

11.1 Independent Clock Source The WWDT can derive its time base from either the 31 kHz LFINTOSC or 31.25 kHz MFINTOSC internal oscillators, depending on the value of WDTE<1:0> Configuration bits. If WDTE = 0b1x, then the clock source will be enabled depending on the WDTCCS<2:0> Configuration bits. If WDTE = 0b01, the SEN bit should be set by software to enable WWDT, and the clock source is enabled by the CS bits in the WDTCON1 register. Time intervals in this chapter are based on a minimum nominal interval of 1 ms. See Section 44.0 “Electrical Specifications” for LFINTOSC and MFINTOSC tolerances. |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 11.2 WWDT működési módok A Windowed Watchdog Timer modulnak négy működési módja van, amelyeket a WDTE <1: 0> bitek vezérelnek a konfigurációs szavakban. Lásd a 11-1. Táblázatot. 11.2.1 A WWDT MINDEN BEÁLLÍTOTT Ha a konfigurációs szavak WDTE bitjei „11” -re vannak állítva, a WWDT mindig be van kapcsolva. A WWDT védelem alvás közben aktív. 11.2.2 A WWDT KÜLÖNLEGES KI Ha a konfigurációs szavak WDTE bitjei „10” -re vannak beállítva, a WWDT be van kapcsolva, kivéve az alvó üzemmódban. A WWDT védelem nem aktív az alvó állapotban. 11.2.3 A SZOFTVER által felügyelt WWDT Ha a konfigurációs szavak WDTE bitjei „01” -re vannak állítva, a WWDT-t a WDTCON0 regiszter SEN bitje vezérli. Az alvó állapotban a WWDT védelem változatlan. További részletekért lásd a 11-1. Táblázatot.

|

11.2 WWDT Operating Modes The Windowed Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 11-1. 11.2.1 WWDT IS ALWAYS ON When the WDTE bits of Configuration Words are set to ‘11’, the WWDT is always on. WWDT protection is active during Sleep. 11.2.2 WWDT IS OFF IN SLEEP When the WDTE bits of Configuration Words are set to ‘10’, the WWDT is on, except in Sleep. WWDT protection is not active during Sleep. 11.2.3 WWDT CONTROLLED BY SOFTWARE When the WDTE bits of Configuration Words are set to ‘01’, the WWDT is controlled by the SEN bit of the WDTCON0 register. WWDT protection is unchanged by Sleep. See Table 11-1 for more details.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 11.3 Időkorlát Ha a WDTCPS <4: 0> konfigurációs bit alapértelmezetten 0b11111, akkor a WDTCON0 regiszter PS bitjei 1 ms-ról 256 másodpercre (névleges) állítják be az időt. Ha az alapértelmezett értéktől eltérő értéket rendel a WDTCPS <4: 0> Konfigurációs bitekhez, akkor az időzítési periódus a CONFIG3L regiszter WDTCPS <4: 0> bitjein alapul. A visszaállítás után az alapértelmezett időtúllépés 2 másodperc. |

11.3 Time-out Period If the WDTCPS<4:0> Configuration bits default to 0b11111, then the PS bits of the WDTCON0 register set the time-out period from 1 ms to 256 seconds (nominal). If any value other than the default value is assigned to WDTCPS<4:0> Configuration bits, then the timer period will be based on the WDTCPS<4:0> bits in the CONFIG3L register. After a Reset, the default time-out period is 2s. |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

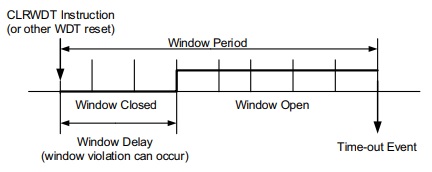

| 11.4 Watchdog ablak A Windowed Watchdog Timer rendelkezik egy opcionális Windowed móddal, amelyet a WDTCW1 <2: 0> konfigurációs bitek és a WDTCON1 regiszter WINDOW <2: 0> bitjei vezérelnek. A Windowed módban a CLRWDT utasításnak a WDT időszak engedélyezett ablakában kell történnie. Bármely CLRWDT utasítás, amely ezen az ablakon kívül történik, egy ablak megsértését váltja ki, és WWDT visszaállítást eredményez, ami hasonló a WWDT időkorlátjához. Egy példát lásd a 11-2. Ábrán. Az ablakméretet a WINDOW <2: 0> Konfigurációs bitek, vagy a WDTCON1 WINDOW <2: 0> bitjei vezérlik, ha WDTCWS <2: 0> = 111. A WDTTMR regiszter öt legjelentősebb bitjét használjuk annak meghatározására, hogy az ablak nyitva van-e, ahogy azt a WDTCON1 regiszter WINDOW <2: 0> bitjei határozzák meg. Ablakszegés esetén egy Reset keletkezik, és a PCON0 regiszter WDTWV bitje törlődik. Ezt a bitet POR állítja be, vagy beállítható firmware-ben. |

11.4 Watchdog Window The Windowed Watchdog Timer has an optional Windowed mode that is controlled by the WDTCWS<2:0> Configuration bits and WINDOW<2:0> bits of the WDTCON1 register. In the Windowed mode, the CLRWDT instruction must occur within the allowed window of the WDT period. Any CLRWDT instruction that occurs outside of this window will trigger a window violation and will cause a WWDT Reset, similar to a WWDT time out. See Figure 11-2 for an example. The window size is controlled by the WINDOW<2:0> Configuration bits, or the WINDOW<2:0> bits of WDTCON1, if WDTCWS<2:0> =111. The five Most Significant bits of the WDTTMR register are used to determine whether the window is open, as defined by the WINDOW<2:0> bits of the WDTCON1 register. In the event of a window violation, a Reset will be generated and the WDTWV bit of the PCON0 register will be cleared. This bit is set by a POR or can be set in firmware. |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 11.5 A WWDT időszámlálója, a WWDT törlődik, ha az alábbi feltételek bármelyike jelentkezik:

|

11.5 Clearing the WWDT The WWDT is cleared when any of the following conditions occur:

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 11.5.1 CLRWDT SZEMPONTOK (WINDOWED MODE) Windowed üzemmódban a WWDT-t élesítenie kell, mielőtt a CLRWDT utasítás leállítja az időzítőt. Ez a WDTCON0 regiszter olvasásával történik. A CLRWDT utasítás végrehajtása anélkül, hogy ilyen élesítési műveletet hajtana végre, az ablak megsértését fogja kiváltani, függetlenül attól, hogy az ablak nyitva van-e vagy sem. További információkért lásd a 11-2. Táblázatot.

|

11.5.1 CLRWDT CONSIDERATIONS (WINDOWED MODE) When in Windowed mode, the WWDT must be armed before a CLRWDT instruction will clear the timer. This is performed by reading the WDTCON0 register. Executing a CLRWDT instruction without performing such an arming action will trigger a window violation regardless of whether the window is open or not. See Table 11-2 for more information.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 11.6 Működés alvó üzemmódban Amikor a készülék alvó üzemmódba lép, a WWDT törlődik. Ha a WWDT alvó üzemmódban van engedélyezve, a WWDT újra számlál. Amikor a készülék kilép az alvó állapotból, a WWDT újra törlődik. A WWDT mindaddig tiszta marad, amíg az Oscillator indítási időzítő (OST) befejeződik, ha engedélyezve van. Az OST-ről további információkért lásd a 7.2.1.3 „Oszcillátor indítási időzítő (OST)” részt. Amikor egy WWDT időtúllépés akkor történik, amikor az eszköz alvó állapotban van, akkor nincs visszaállítás. Ehelyett a készülék felébred és folytatja a működést. A STATUS regiszterben található TO és PD bitek az esemény jelzésére módosulnak. A PCON0 regiszter RWDT bitje is használható. További információkért lásd a 4.0 „Memóriaszervezés” részt. |

11.6 Operation During Sleep When the device enters Sleep, the WWDT is cleared. If the WWDT is enabled during Sleep, the WWDT resumes counting. When the device exits Sleep, the WWDT is cleared again. The WWDT remains clear until the Oscillator Start-up Timer (OST) completes, if enabled. See Section 7.2.1.3 “Oscillator Start-up Timer (OST)” for more information on the OST. When a WWDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. The RWDT bit in the PCON0 register can also be used. See Section 4.0 “Memory Organization” for more information. |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||