- Címlap

- LED kijelzők meghajtása

- Permetező projekt

- PIC18FxxK42

- PIC18FxxK42 I2C regiszterei

- PIC18FxxK42 órajel beállítása

- Pic18FxxK42 regiszterei

- Láb hozzárendelés PIC18FxxK42

- Pic18 I2C programozás

- PIC18FxxK42 I2C kommunikáció

- EEPROM memória használata

- LIN UART-tal fordítás

- LM75A és PIC18F45K42 I2C1 program

- Objektumok

- Pic18FxxK42 konfigurálás

- SPI

- UART PIC18(L)F45K42

- Watchdog Timer

- PIC18F45K42 timer2,-4,-6

- I2C modul 1

- PIC18F45K22 I2C lépései

- PIC18F45K42 USART regiszterei és azok magyarázata II.

- PIC18F45K42 USART regiszterei

- PIC18F45K42 timer1,-3,-5

- UART PIC18F45K42

- PIC18 utasításkészlete

- USART mudullal aszinkron kapcsolat két mikrokontroller közt

- CAN kommunikáció

- DS3231SN RTC

- Dell T 5600

- E-paper

- EGYÉB jegyzet

- ESP 8266 WiFi modul

- ESP-07 ESP-12x

- ESP-12F WiFi modul

- ESP32

- ESP8266

- Egyéb (elektronika)

- Emeléskijelző projekt

- Giroszkóp

- HASZNOSAK

- Hasznos általános linkek

- Illesztő modulok

- Kapcsolások, megoldások

- Kiszajú műveleti erősítő

- Konfigurálás

- LIN kommunikáció UART-tal

- MPASM PIC18

- Nyomásmérés MS5803-05BA-val

- Nyomásmérő I2C

- Nyomásszenzor SPD8xx I2C

- Nyák, nyáktervezés

- Operációs rendszerek

- PIC 18 mikrokontrollerek

- PIC18(L)F47K40

- PIC18(L)F65K40

- PIC18F45(K)50

- PIC18F87k22(80 láb)

- PROGRAMOZÁS

- Programozás

- Python 3

- RAUCH 2057153

- RDS

- RTC TLC 5947-el

- Rádiókapcsolat két mikrokontroller között

- Számítógépes programok

- TCS34725 színérzékelő

- TLC 5947

- TTP223 kapacitív nyomógomb

- USB + USB AN1310-el

- Ulefone Power 2

- Vektoros megszakítások

- Vetőgép

- Webfejlesztés

- WiFi, Bluetooth modulok

- Pickit 3 programozó

- Pic-Ethernet-Pic

- LM75A

- PWM CCPx modullal

- PWM PWMx modullal

- NCO

- TCS 3200 RGB érzékelés

- Nyáktervezés

- Oktatás

- PIC 24 mikrokontrollerek

Konfigurálás

Pic 18F4550 konfigurálása

-------------------------------------------------------------------

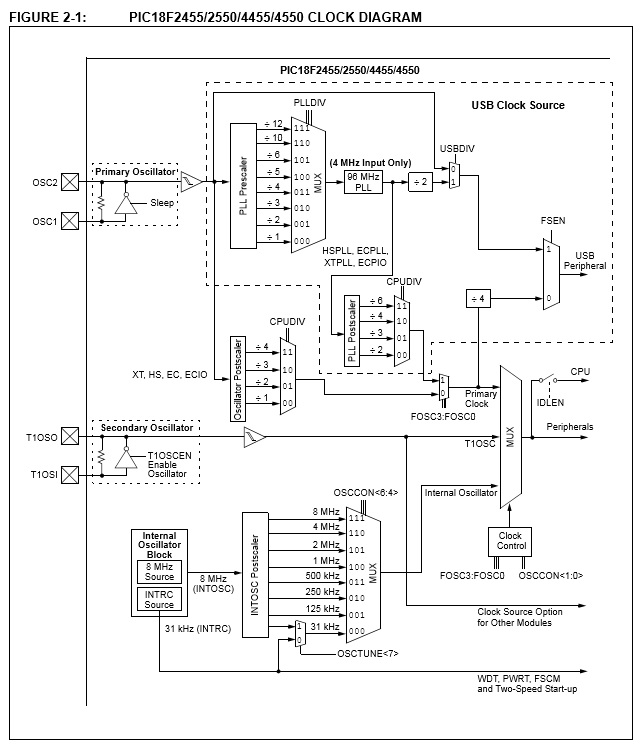

Cím: 300000 Neve: CONFIG1L

| "PLLDIV" beállítása. A valahogyan meglevő elsődleges oszcillátorjel bekerül egy "PLL Prescaler" frekvenciaosztóba, ahonnan 8 különbözű frekvenciájú jel megy a "MUX"-ba, vagyis az adatválaszóba. A 8 különböző frekvenciájú jel közül a "MUX" "PLLDIV" 3 bites adatválasztójával lehet kiválasztani a nekünk megfeleő frekvenciájú jelet. Célszerű ezt 4 Mhz-re beállítani annak érdekében, hogy a kimenetet követő 16 szorozó "PLL" 96 Mhz et adjon, ami egy frekvencia felezőn áthaladva a szükséges 48 Mhz-es USB órajelnet tudja adni a "gyors" USB működéshez (nem USB 3) . Megjegyzem: az USB-nek a lassú üzemmódjához 6 Mhz kell, amit a PDF doksi 24-es oldalán található diadram segítségével tudjuk kiokoskodni, valamint a leírtak megértését is segíti. Sok lehetőség van biztosítva az órajel alakítgatásának és haladási útjának, tehát irány a már említett doksi!, pedig csupán csak az elsődleges oszcillátorról írtam! USB órajel beállító bitre felhívnám a figyelmet: teljes sebességű USB üzemmódban használatos az UCFG:FSEN=1 beállítás. |

|

| Opciók | Magyarázat |

|---|---|

| CONFIG PLLDIV = 1 | "PLL Prescaler" nem változtat a frkvencián. 4 Mhz-es oszcillátorjel esetén ezt célszerű választani. |

| CONFIG PLLDIV = 2 | A "PLL Prescaler" által megfelezett ferkvenciájú jelet válaszjuk a további átalakításokhoz. 8 MHz-es oszcillátorjel esetén ezt célszerű választani. |

| CONFIG PLLDIV = 3 | A "PLL Prescaler" által harmadolt ferkvenciájú jelet válaszjuk a további átalakításokhoz. 12 MHz-es oszcillátorjel esetén ezt célszerű választani. |

| CONFIG PLLDIV = 4 | A "PLL Prescaler" által negyedelt ferkvenciájú jelet válaszjuk a további átalakításokhoz. 16 MHz-es oszcillátorjel esetén ezt célszerű választani. |

| CONFIG PLLDIV = 5 | A "PLL Prescaler" által ötödölt ferkvenciájú jelet válaszjuk a további átalakításokhoz. 20 MHz-es oszcillátorjel esetén ezt célszerű választani20 |

| CONFIG PLLDIV = 6 | A "PLL Prescaler" által hatodolt ferkvenciájú jelet válaszjuk a további átalakításokhoz. 24 MHz-es oszcillátorjel esetén ezt célszerű választani. |

| CONFIG PLLDIV = 10 | A "PLL Prescaler" által tizedelt ferkvenciájú jelet válaszjuk a további átalakításokhoz. 40 MHz-es oszcillátorjel esetén ezt célszerű választani. |

| CONFIG PLLDIV = 12 | A "PLL Prescaler" által tizenkettedelt ferkvenciájú jelet válaszjuk a további átalakításokhoz. 48 MHz-es oszcillátorjel esetén ezt célszerű választani48 |

| "CPUDIV" beállítása. A 'PLLDIV' ben beállított,rendszerint 4 Mhz, majd a megtizenhatszorozott Rendszerint 96 Mhz órajelet a "CPUDIV" osztja le, és ezekből a leosztott jelekből az alábbi leírás alapján választhatjuk ki a CPU órajelet, vagyis a rendszer órajelet. Megjegyzem: az USB órajel is megvalósítható innen egy negyedelőn keresztül alacsony (6 Mhz USB órajel) sebességű üzemmódja esetében. Fontos tudni, hogy a CPU órajel más útvonalon és más forrásból is megvalósítható. |

|

| Opciók | Magyarázat |

| CONFIG CPUDIV = OSC1_PLL2 | Felezi a rendszerint 96 MHz-et, így lesz 48 Mhz |

| CONFIG CPUDIV = OSC1_PLL3 | Harmadolja a rendszerint 96 MHz-et, így lesz 32 Mhz |

| CONFIG CPUDIV = OSC3_PLL4 | Negyedeli a rendszerint 96 MHz-et, így lesz 24 Mhz. Ez alkalmazható egy további negyedelőn keresztül USB lassú működéses lassú USB órajelnek, ami nek 6 MHz-nek kell lenni. Ilyenkor az FSEN=0-nak kell lenni. |

| CONFIG CPUDIV = OSC4_PLL6 | Hatodolja a rendszerint 96 MHz-et, így lesz 16 Mhz |

| UCFG:FSN=1 esetén az USB órajelének beállítása, hogy közvetlenül az elsődleges oszcillátortól vagy ugyanonnan, de a PLLDIV és a 24 szerezőn keresztül kapja meg az órjelet. Mindkét lehetőséget teljes sebességű USB üzemmódban célszerű használni, míg alacsony sebességnél az UCFG:FSN=0 beállítás mellett más útvonal lesz érvényes. | |

| Opciók | Magyarázat |

| CONFIG USBDIV = 0 | USB közvetlenül az elsődleges oszcillátortól kapja az órajelet. Ilyenkor a gyors működéshez célszerű 48 Mhz-es elsődleges oszcillátorfrekvenciát választani. Alacsony sebességű USB üzemmódban pedig 6 Mhz-es elsődleges oszcillátorfrekvencia a célszerű. |

| CONFIG USBDIV = 1 | Az USB a 3 frekvencia átalakítón keresztül kapja az elsődleges oszcillátortól az órajelet. Ilyenkor az elsődleges oszcillátorfrekvencia kevésbé megkötött, mert az osztó és szorzó áramkörök megfelelő konfigurálásával be lehet állítani a kívánt USB órajelet. Ezt az opciót csak magas sebességű USB üzemmódban célszerű használni! |

Cím: 300001 Neve: CONFIG1H

A PIC18 eszközöket tizenkét különböző oszcillátor üzemmódban lehet üzemeltetni. A korábbi PIC18 fokozott mikrokontrollerekkel ellentétben négy ilyen üzemmód közül két oszcillátor típus használható. A felhasználók programozhatják az FOSC3: FOSC0 konfigurációs biteket az alábbi módok egyikének kiválasztására :

Angolul: PIC18 devices can be operated in twelve distinct oscillator modes. In contrast with previous PIC18 enhanced microcontrollers, four of these modes involve the use of two oscillator types Users can program the FOSC3:FOSC0 Configuration bits to select one of these modes:

- XT ------> Kristály vagy kerámia rezonátor (alacsony sebességű) rezgéskeltő

- HS ------> Nagy sebességű kristály vagy kerámia rezonátor rezgéskeltő

- HSPLL -> Nagy sebesséhű kristály vagy kerámia rezonátor rezgéskeltő PLL (frekvenciaosztó áramkör) engedélyezésével

- EC ------> Külső orajel kerül a 13/40-es lábra és megjelenik a 14/40-es lábon a Fosc/4 jel (Fosc/4 = CPU órajelének a negyede, ennyi jel kell egy egyciklusú utasítás végrehajtásához)

- ECIO --> Külső orajelforrás a 13/40-es "CLKO" lábra és a 14/40-es láb "RA6" ilyenkor digitális I/O ként üzemel

- ECPLL -> Külső órajel kerül a 13/40-es "CLKO" lábra PLL (frekvenciaosztó áramkör) engedélyezésével. Ilyenkor a 14/40-es RA6-os lábon a Fosc/4 jelenik meg

- ECPIO -> Külső órajel kerül a 13/40-es "CLKO" lábra PLL (frekvenciaosztó áramkör) engedélyezésével. A 14/40-es láb RA6 ilyenkor digitális I/O ként üzemel

- INTHS -> Belső oszcillátor van használva a CPU órajelánek és nagysebességű (saját elsődleges) oszcillátor van használva USB órajelnek

- INTIO --> Belső oszcillátor van használva a CPU órajelánek és külső orajel kerül a 13/40-es CLKO lábra ami képezi majd az USB órajelet. A 14/40-es láb "RA6" ilyenkor digitális I/O ként üzemel

- INTCKO --> Belső oszcillátor van használva a CPU órajelánek és külső orajelforrás kerül a 13/40-es "CLKO" lábra ami képezi az USB órajelet. Ilyenkor a 14/40-es RA6-os lábon a Fosc/4 jelenik meg

| Oszcillátorok beállítása az USB órajelnek és a CPU órajelne. | |

| Opciók | Magyarázat |

|---|---|

| CONFIG FOSC = HSPLL_HS | Elsődleges oszcillátor van használva CPU és USB órajelnek. a PLLDIV felhasználásával. A HS utal arra, hogy nagysebességű kvarc vagy kerámiarezonátor szükséges ebben a beállításban, ugyanis az oszcillátor erősítője illetve visszacsatolása így működik optimálisan. Lásd a katalógus 25-26 oldalán! |

| CONFIG FOSC = HS | Elsődleges oszcillátor van használva PLLDIV és CPUDIV (:2/:3/:4/:6) nélül, helyette a másik CPUDIV (:1/:2/:3/:4) van használva. Az USB ilyenkor csak alacsony sebességű üzemmódra alkalmas USB órajelet kaphat FSEN=0 beállítással. Valószínűleg FSEN=1 esetén megkaphatja az USB a magasabb órajelet. |

| CONFIG FOSC = INTOSC_HS | Belső oszcillátor van hasznátva CPU órajelnek. Belső oscillátorból van kettő, egy 8Mhz-es és egy RC tagos 31 Khz-es. Az USB órajel az elsődleges HS (gyors) oszcillátorról valósítható meg kvarckristállyal vagy kerámia rezonátorral (INTHS). |

| CONFIG FOSC = INTOSC_XT | Belső oszcillátor van hasznátva CPU órajelnek. Belső oscillátorból van kettő, egy 8Mhz-es és egy RC tagos 31 Khz-es. Az USB órajel az elsődleges XT (lassú) oszcillátorról valósítható meg kvarckristállyal vagy kerámia rezonátorral (INTXT). |

| CONFIG FOSC = INTOSC_EC | Belső oszcillátor van hasznátva CPU órajelnek. Belső oscillátorból van kettő, egy 8Mhz-es és egy RC tagos 31 Khz-es. Az USB órajelhez az órajel az RA6 lábon (CK0-án) külső forrásból jön be további átalakításon keresztül. Rezgéskeltő esetében ide vak csatlakoztatva a rezgéskeltő egyik lába, persze más konfiguráció esetén. Most pedig a kész órajel jön be ezen a lábon további átalakítás után felhasználásra. (INTCK0). |

| CONFIG FOSC = INTOSCIO_EC | Belső oszcillátor van hasznátva CPU órajelnek. Belső oscillátorból van kettő, egy 8Mhz-es és egy RC tagos 31 Khz-es. Az USB órajelhez az órajel az RA6 lábon (CK0-án) külső forrásból jön be további átalakításon keresztül. Rezgéskeltő esetében ide vak csatlakoztatva a rezgéskeltő egyik lába, persze más konfiguráció esetén. Másik megoldás, hogy ide vezetjük a Fosc/4 jelet. Ez a CPU órajelének a negyede, ez alatt hajtódik végre egy rövid utasítás. (INTCK0). |

| CONFIG FOSC = ECPLL_EC | Külső órajelforrás, PLL engedélyezve, CLKO-ként (elsődleges külső órajel bemenete) üzemel a 13/40-es láb, az RA6 (13/40) lábon az Fcy/4 jelenik meg. (ECPLL) |

| CONFIG FOSC = ECPLLIO_EC | Külső órajelfrorrás, PLL engedélyezve, CLKO-ként (elsődleges külső órajel bemenete) üzemel a 13/40-es láb, az RA6 (13/40) láb digitális I/O-ként üzemel. (ECPIO) |

| CONFIG FOSC = EC_EC | Elsődleges oszcillátor használata külső oszcillátor üzemmódban CPU és USB órajelnek. Ilyenkor nem a mikrontroller állítja elő az órajelet, hanem csak a kész órajelet fogadja és dolgozza fel. Tehát, az elsődleges oszcillátor nem működik, csak a kész órajelet fogadja. CLKO-ként üzemel az RA6 (13/40) (EC) |

| CONFIG FOSC = ECIO_EC | Külső órajelforrás az elsődleges oszcillátornál és digitális I/O ként üzemel az RA6 (13/40) láb (ECIO) |

| CONFIG FOSC = XTPLL_XT | XT (lassú frekvenciájú) rezgéskeltő használata az elsődleges oszcillátorrnál és engedélyezve van a PLL (XTPLL) |

| CONFIG FOSC = XT_XT | XT (lassú frekvenciájú) rezgéskeltő használata elsődleges oszcillátornál és nincs engedélyezve a PLL (XT) |

| Opciók | Magyarázat |

| CONFIG FCMEN = OFF | Nem biztonságos idő figyelése kikapcsolva. ????? |

| CONFIG FCMEN = On | Nem biztonságos idő figyelése bekapcsolva. ????? |

| Opciók | Magyarázat |

| CONFIG IESO = OFF | Oszcillátorok átkapcsolhatósága programból nincs engedélyezve |

| CONFIG IESO = On | Oszcillátorok átkapcsolhatósága programból engedélyezve van |

Cím: 300002 Neve: CONFIG2L

| Opciók | Magyarázat |

|---|---|

| CONFIG PWRT = OFF | Bekapcsoláskor nincs (62 msec) várakozás |

| CONFIG PWRT = On | Bekapcsoláskor 62 msec várakozás van |

| Tápfeszültség nagyságának figyelése engedélyezve vagy tiltva lehet a beállítástól függően | |

| Opciók | Magyarázat |

| CONFIG BOR = OFF | Tápfeszültség figyelése tiltva van, így alacsony értéknél nincs reagálás, beavatkozás |

| CONFIG BOR = On | Tápfeszültség figyelése engedélyezve van, így ha a beállított érték alá esik, akkor beavatkozás, reset történik. |

| Opciók | Magyarázat |

| CONFIG BORV = 0 | A maximális 4,59 V-ra van állítva a tápfeszültség figyelési érték. Ha a tápfeszültség 4,59 v-ot nem éri el, akkor RESET keletkezik, ha engedélyezve van |

| CONFIG BORV = 1 | 4,33 V-ra van állítva a tápfeszültség figyelési érték. Ha a tápfeszültség 4,33 V-ot nem éri el, akkor RESET keletkezik, ha engedélyezve van |

| CONFIG BORV = 2 | 2,79V-ra van állítva a tápfeszültség figyelési érték. Ha a tápfeszültség 2,79 V-ot nem éri el, akkor RESET keletkezik, ha engedélyezve van |

| CONFIG BORV = 3 | A minimunra, 2,05 V-ra van állítva a tápfeszültség figyelési érték. Ha a tápfeszültség 2,05 V-ot nem éri el, akkor RESET keletkezik, ha engedélyezve van |

| Opciók | Magyarázat |

| CONFIG VREGEN = OFF | Az USB nem belső feszültségstabilizátorról megy |

| CONFIG VREGEN = On | Az USB belső feszültség stabilizátorról megy |

Cím: 300003 Neve: CONFIG2H

| Opciók | Magyarázat |

|---|---|

| CONFIG WDT = OFF | A watchdog (lefagyás) figyelés ki van kapcsolva |

| CONFIG WDT = ON | A watchdog (lefagyás) figyelés be van kapcsolva. Lefagyás esetén egy beállított érték (idő) után reset keletkezik |

| Opciók | Magyarázat |

| CONFIG WDTPS = 32768 | Watchdog utószámláló beállítása |

| CONFIG WDTPS = 16384 | Watchdog utószámláló beállítása |

| CONFIG WDTPS = 8192 | Watchdog utószámláló beállítása |

| CONFIG WDTPS = 4096 | Watchdog utószámláló beállítása |

| CONFIG WDTPS = 2048 | Watchdog utószámláló beállítása |

| CONFIG WDTPS = 1024 | Watchdog utószámláló beállítása |

| CONFIG WDTPS = 512 | Watchdog utószámláló beállítása |

| CONFIG WDTPS = 256 | Watchdog utószámláló beállítása |

| CONFIG WDTPS = 128 | Watchdog utószámláló beállítása |

| CONFIG WDTPS = 64 | Watchdog utószámláló beállítása |

| CONFIG WDTPS = 32 | Watchdog utószámláló beállítása |

| CONFIG WDTPS = 16 | Watchdog utószámláló beállítása |

| CONFIG WDTPS = 8 | Watchdog utószámláló beállítása |

| CONFIG WDTPS = 4 | Watchdog utószámláló beállítása |

| CONFIG WDTPS = 2 | Watchdog utószámláló beállítása |

| CONFIG WDTPS = 1 | Watchdog utószámláló beállítása |

Cím: 300005 Neve: CONFIG3H

Oszcillátor módok és USB működés:

CPUDIV -> System Clock Postscaler Selection bits

1. opció: OSC1_PLL2

[Primary oscillator Src: /1] [96 MHz PLL Src: /2]

2. opció: OSC2_PLL3

[Primary oscillator Src: /2] [96 MHz PLL Src: /3]

3. opció: OSC3_PLL4

[Primary oscillator Src: /3] [96 MHz PLL Src: /4]

[Ide írhatja a szöveget]

3

CONFIG USBDIV = 1 ; USB Clock Selection bit (used in Full-Speed USB mode only; UCFG:FSEN = 1) (USB clock source comes directly from the primary oscillator block with no postscale)

; CONFIG1H

CONFIG FOSC = EC_EC ; Oscillator Selection bits (EC oscillator, CLKO function on RA6 (EC))

CONFIG FCMEN = OFF ; Fail-Safe Clock Monitor Enable bit (Fail-Safe Clock Monitor disabled)

CONFIG IESO = OFF ; Internal/External Oscillator Switchover bit (Oscillator Switchover mode disabled)

; CONFIG2L

CONFIG PWRT = OFF ; Power-up Timer Enable bit (PWRT disabled)

CONFIG BOR = ON ; Brown-out Reset Enable bits (Brown-out Reset enabled in hardware only (SBOREN is disabled))

CONFIG BORV = 3 ; Brown-out Reset Voltage bits (Minimum setting 2.05V)

CONFIG VREGEN = OFF ; USB Voltage Regulator Enable bit (USB voltage regulator disabled)

; CONFIG2H

CONFIG WDT = ON ; Watchdog Timer Enable bit (WDT enabled)

CONFIG WDTPS = 32768 ; Watchdog Timer Postscale Select bits (1:32768)

; CONFIG3H

CONFIG CCP2MX = ON ; CCP2 MUX bit (CCP2 input/output is multiplexed with RC1)

CONFIG PBADEN = ON ; PORTB A/D Enable bit (PORTB<4:0> pins are configured as analog input channels on Reset)

CONFIG LPT1OSC = OFF ; Low-Power Timer 1 Oscillator Enable bit (Timer1 configured for higher power operation)

CONFIG MCLRE = ON ; MCLR Pin Enable bit (MCLR pin enabled; RE3 input pin disabled)

; CONFIG4L

CONFIG STVREN = ON ; Stack Full/Underflow Reset Enable bit (Stack full/underflow will cause Reset)

CONFIG LVP = ON ; Single-Supply ICSP Enable bit (Single-Supply ICSP enabled)

CONFIG ICPRT = OFF ; Dedicated In-Circuit Debug/Programming Port (ICPORT) Enable bit (ICPORT disabled)

CONFIG XINST = OFF ; Extended Instruction Set Enable bit (Instruction set extension and Indexed Addressing mode disabled (Legacy mode))

; CONFIG5L

CONFIG CP0 = OFF ; Code Protection bit (Block 0 (000800-001FFFh) is not code-protected)

CONFIG CP1 = OFF ; Code Protection bit (Block 1 (002000-003FFFh) is not code-protected)

CONFIG CP2 = OFF ; Code Protection bit (Block 2 (004000-005FFFh) is not code-protected)

CONFIG CP3 = OFF ; Code Protection bit (Block 3 (006000-007FFFh) is not code-protected)

; CONFIG5H

CONFIG CPB = OFF ; Boot Block Code Protection bit (Boot block (000000-0007FFh) is not code-protected)

CONFIG CPD = OFF ; Data EEPROM Code Protection bit (Data EEPROM is not code-protected)

; CONFIG6L

CONFIG WRT0 = OFF ; Write Protection bit (Block 0 (000800-001FFFh) is not write-protected)

CONFIG WRT1 = OFF ; Write Protection bit (Block 1 (002000-003FFFh) is not write-protected)

CONFIG WRT2 = OFF ; Write Protection bit (Block 2 (004000-005FFFh) is not write-protected)

CONFIG WRT3 = OFF ; Write Protection bit (Block 3 (006000-007FFFh) is not write-protected)

; CONFIG6H

CONFIG WRTC = OFF ; Configuration Register Write Protection bit (Configuration registers (300000-3000FFh) are not write-protected)

CONFIG WRTB = OFF ; Boot Block Write Protection bit (Boot block (000000-0007FFh) is not write-protected)

CONFIG WRTD = OFF ; Data EEPROM Write Protection bit (Data EEPROM is not write-protected)

; CONFIG7L

CONFIG EBTR0 = OFF ; Table Read Protection bit (Block 0 (000800-001FFFh) is not protected from table reads executed in other blocks)

CONFIG EBTR1 = OFF ; Table Read Protection bit (Block 1 (002000-003FFFh) is not protected from table reads executed in other blocks)

CONFIG EBTR2 = OFF ; Table Read Protection bit (Block 2 (004000-005FFFh) is not protected from table reads executed in other blocks)

CONFIG EBTR3 = OFF ; Table Read Protection bit (Block 3 (006000-007FFFh) is not protected from table reads executed in other blocks)

; CONFIG7H

CONFIG EBTRB = OFF ; Boot Block Table Read Protection bit (Boot block (000000-0007FFh) is not protected from table reads executed in other blocks)