- Címlap

- LED kijelzők meghajtása

- Permetező projekt

- PIC18FxxK42

- PIC18FxxK42 I2C regiszterei

- PIC18FxxK42 órajel beállítása

- Pic18FxxK42 regiszterei

- Láb hozzárendelés PIC18FxxK42

- Pic18 I2C programozás

- PIC18FxxK42 I2C kommunikáció

- EEPROM memória használata

- LIN UART-tal fordítás

- LM75A és PIC18F45K42 I2C1 program

- Objektumok

- Pic18FxxK42 konfigurálás

- SPI

- UART PIC18(L)F45K42

- Watchdog Timer

- PIC18F45K42 timer2,-4,-6

- I2C modul 1

- PIC18F45K22 I2C lépései

- PIC18F45K42 USART regiszterei és azok magyarázata II.

- PIC18F45K42 USART regiszterei

- PIC18F45K42 timer1,-3,-5

- UART PIC18F45K42

- PIC18 utasításkészlete

- USART mudullal aszinkron kapcsolat két mikrokontroller közt

- CAN kommunikáció

- DS3231SN RTC

- Dell T 5600

- E-paper

- EGYÉB jegyzet

- ESP 8266 WiFi modul

- ESP-07 ESP-12x

- ESP-12F WiFi modul

- ESP32

- ESP8266

- Egyéb (elektronika)

- Emeléskijelző projekt

- Giroszkóp

- HASZNOSAK

- Hasznos általános linkek

- Illesztő modulok

- Kapcsolások, megoldások

- Kiszajú műveleti erősítő

- Konfigurálás

- LIN kommunikáció UART-tal

- MPASM PIC18

- Nyomásmérés MS5803-05BA-val

- Nyomásmérő I2C

- Nyomásszenzor SPD8xx I2C

- Nyák, nyáktervezés

- Operációs rendszerek

- PIC 18 mikrokontrollerek

- PIC18(L)F47K40

- PIC18(L)F65K40

- PIC18F45(K)50

- PIC18F87k22(80 láb)

- PROGRAMOZÁS

- Programozás

- Python 3

- RAUCH 2057153

- RDS

- RTC TLC 5947-el

- Rádiókapcsolat két mikrokontroller között

- Számítógépes programok

- TCS34725 színérzékelő

- TLC 5947

- TTP223 kapacitív nyomógomb

- USB + USB AN1310-el

- Ulefone Power 2

- Vektoros megszakítások

- Vetőgép

- Webfejlesztés

- WiFi, Bluetooth modulok

- Pickit 3 programozó

- Pic-Ethernet-Pic

- LM75A

- PWM CCPx modullal

- PWM PWMx modullal

- NCO

- TCS 3200 RGB érzékelés

- Nyáktervezés

- Oktatás

- PIC 24 mikrokontrollerek

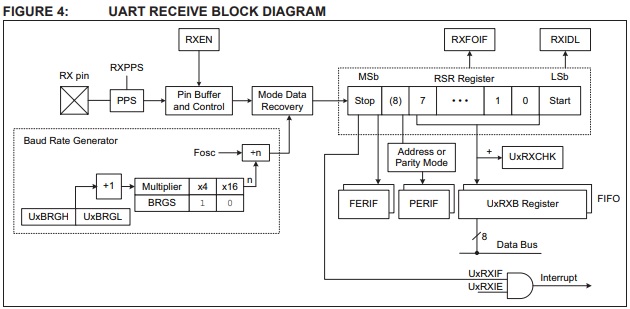

UART PIC18(L)F45K42

Uartnál oszcilloszkópon vizsgálva az 1 alacsony szintű, a 0 marad magas szinten, ugyanis ha nincs adatáramlás, akkor magas szinten van az Rx illetve TX láb. Ami még fontos, hogy adatküldéskor előbb az alacsony helyiértékű bitekket a magasabb helyiértékűek követik. oszcilloszkópon nézve, pont fordítva láthatók (sorrendben is és helyérték szerint is) mint ahogy azt jelöljük.

Hasznos link: https://deepbluembedded.com/uart-pic-microcontroller-tutorial/

UART leírás Pic18-ra (angol): Itt!

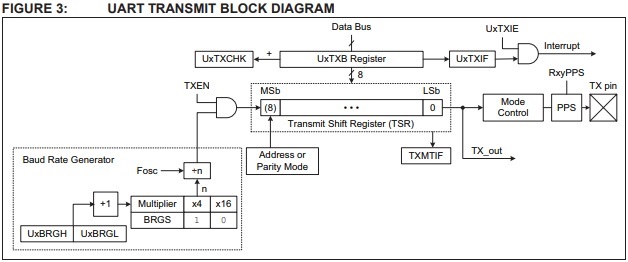

Az átvitelt egy karakter írása az adópufferbe (UxTXB) kezdeményezi. Ha ez az első karakter, vagy az előző karaktert teljesen kiürült a TSR-ből (léptetőregiszterből), akkor az UxTXB-ben lévő adatok azonnal átkerülnek a TSR-be.

Ha a TSR még mindig tartalmaz egy előző karaktert vagy annak egy részét, az új karakteradatokat az UxTXB-ben tárolja, amíg az előző karakterátvitel befejeződik. Az UxTXB-ben várakozó karaktert akkormegy át a TSR-be, miután az előző karakter Stop bitje is elment. A Start bit, az adat bitek és a Stop bit sorozat azonnal elindul, miután befejeződött az előző karakter összes bitje, valamint a Stop bitje is. A TXEN bit 1-re állítása az UxCON0 regiszterben lehetővé teszi az adó számára a jeltovábbítást. Más szóval az UxCON0,TXEN -re állításával indul meg az adás. A TSR az adatbiteket az UxBRGH: UxBRGL regiszterben és az UxCON0 regiszter BRGS bitjében meghatározott felhasználó által meghatározott sebességgel váltja ki. Az UART mód, beleértve a 7-bites, 8 bites, 8 bites címeket vagy paritásokat és a protokoll-támogatási módok bármelyikét, az UxCON0 regiszter MODE <3: 0> bitjein keresztül van kiválasztva.

Az UART átviteli kimenet (TX_out) a Perifériás Pin Select (PPS) modul RxyPPs regiszterén keresztül kiválasztott TX érintkezőn keresztül érhető el. Szintén konfigurálható a szoftverben, mint más, a chipen található perifériák, például a konfigurálható logikai cellák (CLC) bemenetére a megfelelő perifériás regiszteren keresztül. Belső csatlakozás más perifériákhoz, csökkenti a külső kábelezést, és felszabadít néhány pólust (TX érintkező és perifériás bemeneti tű) más célokra.

Két jelző bit használható az adó állapotának meghatározásához: UxTXIF és UxTXMTIF. Az UxTXIF átviteli megszakítási zászló bit minden egyes alkalommal be van állítva, ha az UxTxB üres, függetlenül az UxTXIE átviteli megszakítási engedélyező bit állapotától. Csak akkor világos, ha a TSR egy karakterrel van elfoglalva, és egy új karakter várakozik a továbbításra az UxTXB-ben. Másrészt az UxTXMTIF bit akkor állítható be, ha a TSR üres és üresjáratban van, és törlődik, amikor egy karaktert az UxTXB TSR-re továbbítanak. Ez a két bit végrehajtása attól függően történik, hogy az adatok hogyan íródnak a modulra, amely lehet interrupt alapú vagy polling alapú.

javítani: movf U2ERRIR,F,BANKED ;D:499

U2RTRRIR,TXMTIF

A transmission is initiated by writing a character to the transmit buffer (UxTXB). If this is the first character, or the previous character has been completely flushed from the TSR, the data in the UxTXB is immediately transferred to the TSR.

If the TSR still contains all or part of a previous character, the new character data is held in the UxTXB until the previous character transmission is complete. The pending character in the UxTXB is then transferred to the TSR at the beginning of the previous character Stop bit transmission. The transmission of the Start bit, data bits and Stop bit sequence commences immediately following the completion of all of the previous character’s Stop bits. Setting the TXEN bit in the UxCON0 register enables the transmitter. The TSR shifts data bits out in a rate defined by the user in the UxBRGH:UxBRGL registers and BRGS bit of the UxCON0 register. The UART mode, including the 7-bit, 8-bit, 8-bit with address or parity, and any of the protocol-support modes, is selected throug h the MODE<3:0> bits of the UxCON0 register.

The UART transmit output (TX_out) is available through the TX pin which is selected via the Peripheral Pin Select (PPS) module’s RxyPPs register. It can also be configured in software as an input to other on-chip peripherals such as the Configurable Logic Cell (CLC) through the corresponding peripheral’s register. Internal connection to other peripherals reduces external wiring and also frees up a couple of pins (TX pin and peripheral input pin) for other uses.

Two flag bits can be used to determine the status of the transmitter: UxTXIF and UxTXMTIF. The UxTXIF Transmit Interrupt Flag bit is set whenever the UxTxB is empty, regardless of the state of the UxTXIE transmit interrupt enable bit. It is only clear when the TSR is busy with a character and a new character has been queued for transmission in the UxTXB. On the other hand, the UxTXMTIF bit is set when the TSR is empty and idle, and cleared when a character is transferred to the TSR from the UxTXB. These two bits are implemented depending on how data will be written to the module, which can either be interrupt-based or pollingbased.