- Címlap

- LED kijelzők meghajtása

- Permetező projekt

- PIC18FxxK42

- PIC18FxxK42 I2C regiszterei

- PIC18FxxK42 órajel beállítása

- Pic18FxxK42 regiszterei

- Láb hozzárendelés PIC18FxxK42

- Pic18 I2C programozás

- PIC18FxxK42 I2C kommunikáció

- EEPROM memória használata

- LIN UART-tal fordítás

- LM75A és PIC18F45K42 I2C1 program

- Objektumok

- Pic18FxxK42 konfigurálás

- SPI

- UART PIC18(L)F45K42

- Watchdog Timer

- PIC18F45K42 timer2,-4,-6

- I2C modul 1

- PIC18F45K22 I2C lépései

- PIC18F45K42 USART regiszterei és azok magyarázata II.

- PIC18F45K42 USART regiszterei

- PIC18F45K42 timer1,-3,-5

- UART PIC18F45K42

- PIC18 utasításkészlete

- USART mudullal aszinkron kapcsolat két mikrokontroller közt

- CAN kommunikáció

- DS3231SN RTC

- Dell T 5600

- E-paper

- EGYÉB jegyzet

- ESP 8266 WiFi modul

- ESP-07 ESP-12x

- ESP-12F WiFi modul

- ESP32

- ESP8266

- Egyéb (elektronika)

- Emeléskijelző projekt

- Giroszkóp

- HASZNOSAK

- Hasznos általános linkek

- Illesztő modulok

- Kapcsolások, megoldások

- Kiszajú műveleti erősítő

- Konfigurálás

- LIN kommunikáció UART-tal

- MPASM PIC18

- Nyomásmérés MS5803-05BA-val

- Nyomásmérő I2C

- Nyomásszenzor SPD8xx I2C

- Nyák, nyáktervezés

- Operációs rendszerek

- PIC 18 mikrokontrollerek

- PIC18(L)F47K40

- PIC18(L)F65K40

- PIC18F45(K)50

- PIC18F87k22(80 láb)

- PROGRAMOZÁS

- Programozás

- Python 3

- RAUCH 2057153

- RDS

- RTC TLC 5947-el

- Rádiókapcsolat két mikrokontroller között

- Számítógépes programok

- TCS34725 színérzékelő

- TLC 5947

- TTP223 kapacitív nyomógomb

- USB + USB AN1310-el

- Ulefone Power 2

- Vektoros megszakítások

- Vetőgép

- Webfejlesztés

- WiFi, Bluetooth modulok

- Pickit 3 programozó

- Pic-Ethernet-Pic

- LM75A

- PWM CCPx modullal

- PWM PWMx modullal

- NCO

- TCS 3200 RGB érzékelés

- Nyáktervezés

- Oktatás

- PIC 24 mikrokontrollerek

LIN UART-tal fordítás

Nagyon jó dokumentáció: http://www.t-es-t.hu/download/microchip/an235a.pdf

Dokumentáció 480. old.: itt!

Fordító: http://magyar-angol-szotar.hu

| 31.5. LIN módok (csak UART1) D: 494. old. A LIN egy olyan protokoll, amelyet elsősorban az autóiparban használnak. A LIN hálózat kétféle szoftverfolyamatból áll: egy master folyamatból és egy szolga folyamatból. Minden hálózatnak csak egy mestere és egy vagy több szolga folyamata van. Fizikai réteg szempontjából mikrokontroller egyik UART-ját (UART1) mind a master, mind a szolga folyamat vezérelheti mindaddig, amíg csak egy mester folyamat létezik a hálózaton. A LIN tranzakció egy mester folyamatból áll, amelyet egy szolga folyamat követ. A szolga folyamat egynél több szolgát is magában foglalhat, ahol az egyik továbbítja, a másik vagy másikok fogadják a jeleket. A tranzakció a következő mastervezérelt folyamatátviteli sorrendben kezdődik: 1. Törés 2. Határoló bit 3. Szinkronizálási mező 4. PID bájt A PID meghatározza, hogy melyik szolgaválaszol a mesternek . Amikor a PID bájt befejeződik, a TX kimenet az üresjárati állapotban marad. A szolgák közül egy vagy több válaszolhat a mester folyamatra. Ha senki nem válaszol az 1 bites időszakon belül, a Mester szabadon indíthat egy másik új adást. A bájtidőszakot az UART-tól eltérő eszközzel időzítettük. A Slave folyamat követi a Master folyamatot. Amikor a Slave szoftveresen felismeri a PID-et, akkor a Slave-folyamat válaszol a kívánt válasz továbbításával vagy a továbbított adatok fogadásával. Csak Slave folyamatok adnak adatokat. Ezért a Slave folyamatok, amelyek adatokat kapnak, egy másik Slave folyamatot kapnak. Amikor egy Slave adatot küld, a Slave UART automatikusan kiszámítja az ellenőrzött összeget az elküldött bájtokhoz, ahogy azok elküldésre kerülnek, és a fordított ellenőrzőösszeg bájtot hozzáadja a slave válaszhoz. Amikor egy Slave adatokat fogad, az ellenőrző összeget minden bájtban felhalmozzák, ahogy azt a küldő folyamathoz hasonló algoritmus segítségével fogadják. Az utolsó bájt, amely a küldő folyamat által kiszámított invertált ellenőrzőösszeg, hozzáadódik az UART által számított helyi számításhoz. Az ellenőrzés akkor megy végbe, amikor az eredmény mindegyike „1”, ellenkező esetben az ellenőrzés sikertelen és a CERIF bit 1-re áll be. Az ellenőrző összeg kiszámításához két módszer áll rendelkezésre: örökölt és továbbfejlesztett. Az örökölt ellenőrző összeg csak az adat bájtokat tartalmazza. A továbbfejlesztett ellenőrző összeg tartalmazza a PID-t és az adatokat. Az UxCON2 regiszterben lévő C0EN vezérlőbit meghatározza az ellenőrzőösszeg módszert. A C0EN beállítása „1” -re választja ki a továbbfejlesztett módszert. A szoftvernek ki kell választania a megfelelő módszert, mielőtt az ellenőrző összeg bájtja kiértékelődik. |

31.5 LIN Modes (UART1 only) LIN is a protocol used primarily in automotive applications. The LIN network consists of two kinds of software processes: a Master process and a Slave process. Each network has only one Master process and one or more Slave processes. From a physical layer point of view, the UART on one processor may be driven by both a Master and a Slave process, as long as only one Master process exists on the network. A LIN transaction consists of a Master process followed by a Slave process. The lave process may involve more than one Slave where one is transmitting and the other(s) are receiving. The transaction begins by the following Master process transmission sequence: 1. Break 2. Delimiter bit 3. Sync Field 4. PID byte The PID determines which Slave processes are expected to respond to the Master. When the PID byte is complete, the TX output remains in the Idle state. One or more of the Slave processes may respond to the Master process. If no one responds within the inter-byte period, the Master is free to start another transmission. The inter-byte period is timed by software using a means other than the UART. The Slave process follows the Master process. When the Slave software recognizes the PID then that Slave process responds by either transmitting the required response or by receiving the transmitted data. Only Slave processes send data. Therefore, Slave processes receiving data are receiving that of another Slave process. When a Slave sends data, the Slave UART automatically calculates the checksum for the transmitted bytes as they are sent and appends the inverted checksum byte to the slave response. When a Slave receives data, the checksum is accumulated on each byte as it is received using the same algorithm as the sending process. The last byte, which is the inverted checksum value calculated by the sending process, is added to the locally calculated checksum by the UART. The check passes when the result is all ‘1’s, otherwise the check fails and the CERIF bit is set. Two methods for computing the checksum are available: legacy and enhanced. The legacy checksum includes only the data bytes. The enhanced checksum includes the PID and the data. The C0EN control bit in the UxCON2 register determines the checksum method. Setting C0EN to ‘1’ selects the enhanced method. Software must select the appropriate method before the Start bit of the checksum byte is received. |

| 31.5.2. LIN SLAVE MODE A LIN Slave mód a következő beállításokkal állítható be: • UxCON0<MODE> (<3: 0>) = 1011 • UxCON0<TXEN> = 1 • UxCON0<RXEN> = 1 • UxP2 = Az átvitt adat bájtok száma • UxP3 = A fogadott adat bájtok száma • UxBRGH: L = Érték az alapértelmezett átviteli sebesség eléréséhez • UxCON2<TXPOL> = 0 (Forbított polaritással használjuk az adatvonalat. Ha sokat van az eszköz idle állapotban) • <UxCON0>STP = kívánt Stop bit kiválasztása • <UxCON0>C0EN = kívánt ellenőrzőösszeg mód • RxyPPS = TX pin kiválasztási kód • TX TRIS vezérlés = 0 (TRISx regiszter TX kimenetnek) • <UxCON1>ON = 1 A Slave folyamat akkor kezdődik, amikor a RX bemezeten a jelszint megváltozik a break jel megjelenésével. A break törli az UxTXCHK, az UxRXCHK, az UxP2 és az UxP3 regisztereket. A break végén az automatikus adatkapcsolati üzemmód aktiválódik, és az átviteli sebesség (baud) automatikusan megállapításra és beállításra kerül a break (szünet) utáni 0x55 szinkronizáló karaktar karakter felhasználásával. A Szinkronizáló karaktert követő karakter PID kódként érkezik, és a fogadott FIFO-ban kerül mentésre. Az UART kiszámítja a két PID paritásbitet a PID hat legalacsonyabb hilyiértékű bitéből. Ha bármelyik paritásbit nem felel meg a kapott PID-kód megfelelő bitjének, akkor a UxERRIR<PERIF> bitet 1-re állítja, és a kiszámolt két hibajelző bittel és a PID kóddal együtt a FIFO-ba teszi be és ott tárolja. Ha a paritásbitek megfelelnek a kapott PID-kód megfelelő bitjének, akkor a UxERRIR<PERIF> bit 0-át jelez. Ezt követően a PIR3<U1RXIF> bit 1-re beáll jelezve, hogy a PID elérhető. Szerintem paritáshiba esetén is és az nélkül is mindez megtörténik az U1RXIF bittel Ezért szerintem ezen bit beállta után kell kiértékelni az UxERRIR<PERIF> bitet. A szoftver az UxRXB regiszter elolvasásával lekéri a PID-et, és szofrveresen meghatározzuk a szolga folyamatot, amelyet végre kell hajtani. Az ellenőrzőösszeg módszerét, a bájtok számát, valamint az adatok küldését vagy fogadását a PID kódból programból mi határozzuk meg. |

31.5.2 LIN SLAVE MODE LIN Slave mode is configured by the following settings: • MODE<3:0> = 1011 • TXEN = 1 • RXEN = 1 • UxP2 = Number of data bytes to transmit • UxP3 = Number of data bytes to receive • UxBRGH:L = Value to achieve default baud rate • TXPOL = 0 (for high Idle state) • STP = desired Stop bits selection • C0EN = desired checksum mode • RxyPPS = TX pin selection code • TX pin TRIS control = 0 • ON = 1 The Slave process starts upon detecting a Break on the RX pin. The Break clears the UxTXCHK, UxRXCHK, UxP2, and UxP3 registers. At the end of the Break, the auto-baud circuity is activated and the baud rate is automatically set using the Sync character following the Break. The character following the Sync character is received as the PID code and is saved in the receive FIFO. The UART computes the two PID parity bits from the six Least Significant bits of the PID. If either parity bit does not match the corresponding bit of the received PID code, the PERIF flag is set and saved at the same FIFO location as the PID code. The UxRXIF bit is set indicating that the PID is available. Software retrieves the PID by reading the UxRXB register and determines the Slave process to execute from that. The checksum method, number of ata bytes, and whether to send or receive data, is defined by software according to the PID code. |

| 31.12. Áramlásszabályozás Ez a rész nem vonatkozik a LIN, DALI vagy DMX üzemmódokra. Az áramlásszabályozás az az eszköz, amellyel a küldő UART adatfolyamot egy fogadó UART felfüggesztheti. Az áramlásszabályozás megakadályozza a bemeneti pufferek túlcsordulását szoftver beavatkozás nélkül. Az UART támogatja mind a hardvert, mind az XON / XOFF nekem az áramlásszabályozót. Az áramlásszabályozási módot az UxCON2 regiszter FLO <1: 0> bitjei választják ki. Az áramlásszabályozás le van tiltva, ha mindkét bit törlődik. |

31.12 Flow Control This section does not apply to the LIN, DALI, or DMX modes. Flow control is the means by which a sending UART data stream can be suspended by a receiving UART. Flow control prevents input buffers from overflowing without software intervention. The UART supports both hardware and XON/XOFF me thods of flow control. The flow control method is selected with the FLO<1:0> bits in the UxCON2 register. Flow control is disabled when are both bits are cleared. |

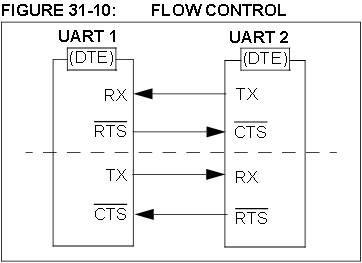

| 31.12.1. HARDWARE FLOW CONTROL A hardveráramlás-vezérlést úgy választjuk meg, hogy az FLO <1: 0> biteket 10-re állítjuk. A hardveráramlás-szabályozás három lehetőségből áll. Ezek közül az RS-232 jelek az RTS és a CTS. Mindkettő alacsony. A harmadik sor egy RS-485 adó-vevő vezérlésére használható. Ennek a jelnek a neve a TXDE az adásvezérléshez. Ez a kimenet magas, ha a TX kimenet karaktert küld, és minden más alkalommal alacsony. Az UART DTE (számítógép) eszközként van konfigurálva, ami azt jelenti, hogy az RTS kimenet, a CTS pedig bemenet. Az RTS és a CTS jelek párként működnek az átviteli áramlás szabályozására. A DTE-DTE konfiguráció összekapcsolja a fogadó UART RTS kimenetét a küldő UART CTS bemenetével. Lásd a 31-10. Ábrát. Az UART fogadó adat az RTS kimenetet alacsonyra állítja, amikor a bemenet FIFO üres. Amikor egy karakter érkezik, az RTS kimenet magas, amíg az UxRXB leolvasásra kerül, hogy felszabadítsa mindkét FIFO helyet. Amikor a CTS bemenet magas, miután a bájt elkezdte továbbítani, az átvitel normálisan befejeződik. A fogadó eszköz ezt a karaktert a második FIFO ?helyszínen fogadja el?, még akkor is, ha a CTS bemenet magas. |

31.12.1 HARDWARE FLOW CONTROL Hardware flow control is selected by setting the FLO<1:0> bits to ‘10’. Hardware flow control consists of three lines. The RS-232 signal names for two of these are RTS, and CTS. Both are low true. The third line may be used to control an RS-485 transceiver. The signal name for this is TXDE for transmit drive ena ble. This output is high when the TX output is acti vely sending a character and low at all other times. The UART is configured as DTE (computer) equipment which means RTS is an output and CTS is an input. The RTS and CTS signals work as a pair to control the transmission flow. A DTE-to-DTE configuration connects the RTS output of the receiving UART to the CTS input of the sending UART. Refer to Figure 31-10. The UART receiving data asserts the RTS output low when the input FIFO is empty. When a character is received, the RTS output goes high until the UxRXB is read to free up both FIFO locations. When the CTS input goes high after a byte has started to transmit, the transmission will complete normally. The receiver accommodates this by accepting the character in the second FIFO location even when the CTS input is high. |

| 31.12.2. RS-485 TRANSCEIVER CONTROL A hardveráramlás-szabályozás használható az RS-485 adó-vevő irányának vezérlésére, amint azt a 31-11. Ábra mutatja. Konfigurálja a CTS bemenetet, amelyet mindig engedélyezni kell, ha az UxCTSPPS kiválasztást egy nem végrehajtott porttűre, például az RD0-ra állítja. Amikor a jel- és vezérlővonalak a 31-11. Ábrán láthatóak, akkor az UART nem kap saját adást. Annak ellenőrzésére, hogy nincs-e ütközés az RS-485 vonalakon, akkor az adó-vevő RE vezérlése leválasztható a TXDE-ről és alacsonyan kötődhet, ezáltal lehetővé teszi az összes adás hurok-visszavételét. További információkért lásd: 31.14. Szakasz „Az ütközésérzékelés”. |

31.12.2 RS-485 TRANSCEIVER CONTROL Hardware flow control can be used to control the direction of an RS-485 transceiver as shown in Figure 31-11. Configure the CTS input to be always enabled by setting the UxCTSPPS selection to an unimplemented port pin such as RD0. When the signal and control lines are configured as shown in Figure 31-11, then the UART will not receive its own transmissions. To verify that there are no collisions on the RS-485 lines then the transceiver RE control can be disconnected from TXDE and tied low thereby enabling loop-back reception of all transmissions. See Section 31.14 “Collision Detection” for more information. |

|

|

| 31.12.3. XON / XOFF FLOW CONTROL Az XON / XOFF áramlásszabályozása úgy van kiválasztva, hogy az FLO <1: 0> biteket 01-re állítja. Az XON / XOFF egy adat alapú áramlásszabályozási módszer. Az átvitel felfüggesztésére és folytatására szolgáló jelek a vevő által az adónak küldött speciális karakterek. Az előnye, hogy további hardvervonalakra nincs szükség. Az XON / XOFF áramlásszabályozás teljes duplex műveletre van szükség, mert az adónak képesnek kell lennie arra, hogy fogadja a jelet a továbbítás felfüggesztéséhez, miközben az adás folyamatban van. Bár az XON és az XOFF nincs meghatározva az ASCII kódban, az általánosan elfogadott értékek az XOFF esetében 13 óra és az XON esetében 11 óra. Az UART ezeket a kódokat használja. Az adó alapértelmezés szerint XON, vagy engedélyezett. Ezt az állapotot az UxFIFO regiszterben csak az ead-csak XON bit jelzi. Ha XOFF karaktert kap, az adó nem továbbítja az adást az aktívan továbbított karakter befejezése után. Az adóegység addig marad érvényben, amíg nem érkezik XON karakter. Az XON akkor lesz kényszerítve, ha a szoftver átvált a TXEN bitre. Amikor az UxCON2 regiszterben található RUNOVF bit be van állítva, a XON és az XOFF karakterek továbbra is fogadásra és feldolgozásra kerülnek anélkül, hogy az UxRXB olvasásával el kellene távolítani a bemenet FIFO-t. Ha azonban a RUNOVF bit tiszta, akkor az UxRXB-t le kell olvasni, hogy elkerüljük a vételi túlcsordulást, amely felfüggeszti az áramlásszabályozást, amikor a vételi puffer túlcsordul. |

31.12.3 XON/XOFF FLOW CONTROL XON/XOFF flow control is selected by setting the FLO<1:0> bits to ‘01’. XON/XOFF is a data based flow control method. The signals to suspend and resume transmission are special characters sent by the receiver to the transmitter The advantage is that additional hardware lines are not needed. XON/XOFF flow control re quires full duplex operation because the transmitter must be able to receive the signal to suspend transmitting while the transmission is in progress. Although XON and XOFF are not defined in the ASCII code, the gener ally accepted values are 13h for XOFF and 11h for XON. The UART uses those codes. The transmitter defaults to XON, or transmitter enabled. This state is also indicated by the ead-only XON bit in the UxFIFO register. When an XOFF character is received, the transmitter stops transmitting after completing the character actively being transmitted. The transmitter remains disabled until an XON character is received. XON will be forced on when software toggles the TXEN bit. When the RUNOVF bit in the UxCON2 register is set then XON and XOFF char acters continue to be received and processed without the need to clear the input FIFO by reading the UxRXB. However, if the RUNOVF bit is clear then the UxRXB must be read to avoid a receive overflow which will suspend flow control when the receive buffer overflows. |

| 31.13. Ellenőrző összeg (csak UART1) Ez a rész nem vonatkozik a LIN módra, amely automatikusan ellenőrzi az ellenőrző összegeket. Az átviteli és fogadó ellenőrzőösszeg-adalékok engedélyezve vannak, ha a C0EN bit az UxCON2 regiszterben van beállítva. Ha engedélyezve van, a hozzáadók összegyűjti az átadott vagy fogadott minden bájtot. A felhalmozott összeg tartalmazza a kiegészítés átvitelét. A szoftver a tranzakció előtt felelős az ellenőrző összeg-nyilvántartások törléséért és a tranzakció végén az ellenőrzés elvégzéséért. Az alábbiakban bemutatjuk, hogyan lehet az ellenőrzőösszeg-regisztereket aszinkron módokban használni. 31.13.1. ÁTMENETI ELLENŐRZÉS MÓDSZER

31.13.2 AZ ELLENŐRZÉS ELLENŐRZÉSI MÓDSZERE

A CERIF ellenőrzőösszeg megszakító jelzője nem aktív a LIN-n kívül más módban.. |

31.13 Checksum (UART1 only) This section does not apply to the LIN mode, which handles checksums automatically. The transmit and receive checksum adders are enabled when the C0EN bit in the UxCON2 register is set. When enabled, the adders accumulate every byte that is transmitted or received. The accumulated sum includes the carry of the addition. Software is responsible for clearing the checksum registers before a transaction and performing the check at the end of the transaction. The following is an exam ple of how the checksum registers could be used in the asynchronous modes. 31.13.1 TRANSMIT CHECKSUM METHOD

The CERIF checksum interrupt flag is not active in any mode other than LIN. |

| 31.14. Ütközésérzékelés Az átviteli vonallal érintkező külső erőket minden működési módban az ütközésérzékeléssel észlelik. Az ütközésérzékelés mindig aktív, ha mindkettő RXEN és TXEN van beállítva. Ha a beérkező bemenet ugyanazon az I / O-érintkezőn vagy külső áramkörön keresztül kapcsolódik az adó kimenethez, akkor minden egyes továbbított karakterhez egy karakter érkezik. Az ütközésérzékelő áramkör figyelmeztetést ad, ha a kapott szó nem egyezik a továbbított szóval. Az Ux ERRIR regiszterben lévő TXCIF jelzőt az ütközések jelzésére használják. Ez a jel csak akkor hasznos, ha a TX kimenet vissza van kapcsolva a RX bemenetre, és minden, ami továbbításra kerül, várhatóan fogadásra kerül. Ha egyidejűleg több adó is aktív, akkor feltételezhető, hogy a TX szó nem egyezik meg az RX szóval. A TXCIF észleli ezt az eltérést és jelzi a megszakítást. A TXCIF bit is DALI módú átvitelekben lesz beállítva, amikor a fogadott bit hiányzik a várható közepes bites átmenetről. Az ütközésérzékelés mindig aktív, függetlenül attól, hogy az RX bemenet csatlakozik-e a TX kimenethez. A felhasználó feladata, hogy letiltja a TXCIE bitet, amikor az ütközési megszakítások nem szükségesek. Az átvitt adatok fogadó pufferének kirakodásakor a szoftver felülírása elkerülhető úgy, hogy az UxCON2-ben beállítja a RUNOVF bitet, és figyelmen kívül hagyja a vételi megszakítást és hagyja, hogy a fogadó puffer túlcsorduljon. Amikor az adatátvitel befejeződött, készítse elő az adatok fogadását a fogadó puffer öblítésével (lásd 31.11.2. Szakasz, FIFO visszaállítás) és az RXFOIF túlcsordulás jelző törlését az UxERRIR regiszterben. |

31.14 Collision Detection External forces that interf ere with the transmit line are detected in all modes of operation with collision detection. Collision detection is always active when RXEN and TXEN are both set. When the receive input is connected to the transmit output through either the same I/O pin or external circuitry, a character will be received for every character transmitted. The collision detection circuit provides a warning when the word received does not match the word transmitted. The TXCIF flag in the Ux ERRIR register is used to signal collisions. This signal is only useful when the TX output is looped back to the RX input and everything that is transmitted is expected to be received. If more than one transmitter is active at the same time, it can be assumed that the TX word will not match the RX word. The TXCIF detects this mismatch and flags an interrupt. The TXCIF bit will also be set in DALI mode transmissions when the received bit is missing the expected mid-bit transition. Collision detection is always active, regardless of whether or not the RX input is connected to the TX output. It is up to the user to disable the TXCIE bit when collision interrupts are not required. The software overhead of unloading the receive buffer of transmitted data is avoided by setting the RUNOVF bit in UxCON2 and ignoring the receive interrupt and letting the receive buffer overflow. When the transmission is complete, prepare for receiving data by flushing the receive buffer (see Section 31.11.2, FIFO Reset) and clearing the RXFOIF overflow flag in the UxERRIR register. |

| 31.15. RX / TX aktivitási időtúllépés Az UART a HLT időzítőkkel együttműködve figyelemmel kíséri az RX és TX vonalak működését. Ezzel a funkcióval határozhatja meg, hogy a vevő vagy az átviteli vonalakon nincs-e aktivitás a felhasználó által meghatározott időtartamra. A funkció használatához állítsa be a HLT-t a kívánt időkorlátra a HLT óraforrás, az időzítő előre beállított értéke és az időzítő-regiszterek kombinációjával. Állítsa be a HLT-t az UART TX vagy RX vonalon alaphelyzetbe állításához, és indítsa el a HLT-t az UART indításakor. Az UART tevékenység folytatja a HLT visszaállítását, hogy megakadályozzák a teljes HLT időtartam eltűnését. Ha a kiválasztott TX vagy RX vonalon nem volt aktivitás hosszabb ideig, mint a HLT periódus, akkor egy HLT megszakítás történik, amely jelzi az időtúllépés eseményét. Például a következő regiszterbeállítások lesznek konfigurálja a HLT2-t az U1RX-en végzett tevékenység 5 ms-os időtúllépésére: • T2PR = 0x9C (156 előre beállított idő) • T2CLKCON = 0x05 (500 kHz belső oszcillátor) • T2HLT = 0x04 (szabad futás, az emelkedő szélén alaphelyzetbe állítás) • T2RST = 0x15 (alaphelyzetbe állítás az U1RX-en) • T2CON = 0xC0 (Timer2 bekapcsolva 1:16 előrejelzéssel) |

31.15 RX/TX Activity Timeout The UART works in conjunction with the HLT timers to monitor activity on the RX and TX lines. Use this feature to determine when there has been no activity on the receive or transmit lines for a user specified period of time. To use this feature, set the HLT to the desired timeout period by a combination of the HLT clock source, timer prescale value, and timer period registers. Configure the HLT to reset on the UART TX or RX line and start the HLT at the same time the UART is started. UART activity will keep resetting the HLT to prevent a full HLT period from elapsing. When there has been no activity on the selected TX or RX line for longer than the HLT period then an HLT interrupt will occur signaling the timeout event. For example, the following register settings will configure HLT2 for a 5 ms timeout of no activity on U1RX: • T2PR = 0x9C (156 prescale periods) • T2CLKCON = 0x05 (500 kHz internal oscillator) • T2HLT = 0x04 (free running, reset on rising edge) • T2RST = 0x15 (reset on U1RX) • T2CON = 0xC0 (Timer2 on with 1:16 prescale) |

| ; Példa az időtúllépés figyelésére (asm) Pic18FxK42: ; Megj.: Szerintem nem ccak a Tmr2, a Tmr4 vagy Tmr6 is lehet banksel T2PR ; T2PR = 0x9C (156 előre beállított idő) movlw h'9c' ; Javasolt: 9C=156 (5 ms-os időtúllépésére) movwf T2PR,BANKED ; banksel T2CLKCON ; movlw h'05' ; 0x05 (500 kHz belső oszcillátor) movwf T2CLKCON,BANKED ; banksel T2HLT ; movlw h'04' ; = 0x04 (szabad futás, az emelkedő szélén alaphelyzetbe állítás) movwf T2HLT,BANKED ; banksel T2RST ; D: 336. old. T4RST vagy T6RST is lehet movlw h'15' ; (alaphelyzetbe állítás az U1RX-en) ; Választani az igény szerint movlw h'16' ; (alaphelyzetbe állítás az U1TX-en) ; Választani az igény szerint movwf T2RST,BANKED ; (alaphelyzetbe állítás az U1RX-en) banksel T2CON ; T2CON,ON<7> movlw h'c0' ; 0xC0 (Timer2 bekapcsolva 1:16 előrejelzéssel) movwf T2CON,BANKED ; ; bcf T2CON,ON_T2CON ; T: Ne legyen időtőllépés figyelés pld.: teszteléskor |

|

| 31.17.1. AUTO-BAUD DETECT Az UART modul támogatja az átviteli sebesség automatikus észlelését és kalibrálását a 8 bites aszinkron és LIN üzemmódokban. Az ABDEN beállítása az autobaud érzékelés elindításához nem szükséges, sót LIN módban nem is lehetséges, mert ez az üzemmód automatikusan támogatja az automatikus baudsebesség megállapítását és beállítását minden egyes adatcsomag elején. Az automatikus átviteli érzékelés engedélyezése az ABDEN bit használatával csak az aszinkron üzemmódokra vonatkozik, a LIN üzemmódra nem. Megjegyzés: DALI módban az ABDEN figyelmen kívül marad. A bitsebességet manuálisan 1200-ra kell beállítani a BRG regiszterek használatával. Ha az Auto-Baud Detect (ABD) aktív, a BRG órája megfordul. A bejövő RX jelet a BRG-nek nem az órajel, hanem a BRG időzíti. A Baud Rate Generatort arra használják, hogy a fogadott 55 órás (ASCII „U”) periódust, amely a LIN busz szinkron karaktere, időzíti. Ennek a karakternek az egyedülálló jellemzője, hogy öt eső éllel rendelkezik, beleértve a Start bit szélét, és öt emelkedő élet, beleértve a Stop bit szélét is. 8 bites aszinkron üzemmódban az UxCON0<ABDEN> bit beállítása az UxCON0 regiszterben lehetővé teszi az automatikus átviteli kalibrációs sorozatot. Az UxCON0<ABDEN> beállítása után az RX bemenet első leeső éle elindítja az automatikus átviteli kalibrációs szekvenciát. Miközben az ABD szekvencia megtörténik, az UART üresjáratban van. A fogadóvonal első leeső szélén az UxBRG a BRG számláló órával kezd számolni, ahogy a 31-12. ábrán látható. Az ötödik leeső él a 7-es bázis időszak elején az RX-bemeneten fog megjelenni. Abban az időben az UxBRGH, az UxBRGL regiszterpárban a megfelelő BRG periódust összegyűjtött halmozott érték marad, az UxCON0<ABDEN> bit automatikusan törlődik és az ABDIF megszakítás jelzője be van állítva. Az ABDIF bitet szoftverből kell törölni. Az RXIDL azt jelzi, hogy a szinkronizálás bemenet aktív. Az RXIDL alacsony lesz az első leeső szélén, és magas szintre vált az ötödik emelkedő élen. A BRG automatikus átviteli óráját a BRGS bit határozza meg a 31-2. Táblázat szerint. Az ABD alatt a belső BRG regisztert 16 bites számlálóként használják. Az UxBRGH és az UxBRGL regiszterek azonban megtartják az előző BRG értéket, amíg az automatikus átviteli folyamat sikeresen befejeződik. Miközben kalibrálja az adatátviteli sebességet, a belső BRG regisztert a BRG bázisóra sebességének 1/8-as órájával kell órajelezni. A kapott bájtmérés az átlagos bites idő, amikor teljes sebességgel van órajelezve, és a teljes UxBRGH és UxBRGL regiszterekbe kerül. Megjegyzés:

|

31.17.1 AUTO-BAUD DETECT The UART module supports automatic detection and calibration of the baud rate in the 8-bit asynchronous and LIN modes. However, setting ABDEN to start autobaud detection is neither necessary, nor possible in LIN mode because that mode supports auto-baud detection automatically at the beginning of every data packet. Enabling auto-baud detect with the ABDEN bit applies to the asynchronous modes only. Note: In DALI Mode, ABDEN is ignored. The baud rate needs to be manually set to 1200 using the BRG registers. When Auto-Baud Detect (ABD) is active, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII “U”), which is the Sync character for the LIN bus. The unique feature of this character is that it has five falling edges, including the Start bit edge, five rising edges including the Stop bit edge. In 8-bit Asynchronous mode, setting the ABDEN bit in the UxCON0 register enables the auto-baud calibration sequence. The first falling edge of the RX input after ABDEN is set will start the auto-baud calibration sequence. While the ABD sequence takes place, the UART state machine is held in idle. On the first falling edge of the receive line, the UxBRG begins counting up using the BRG counter clock as shown in Figure 31-12. The fifth falling edge will occur on the RX pin at the beginning of the bit 7 period. At that time, an accumulated value totaling the proper BRG period is left in the UxBRGH, UxBRGL register pair, the ABDEN bit is automatically cleared and the ABDIF interrupt flag is set. ABDIF must be cleared by software. RXIDL indicates that the sync input is active. RXIDL will go low on the first falling edge and go high on the fifth rising edge. The BRG auto-baud clock is determined by the BRGS bit as shown in Table 31-2. During ABD, the internal BRG register is used as a 16-bit counter. However, the UxBRGH and UxBRGL registers retain the previous BRG value until the auto-baud process is successfully completed. While calibrating the baud rate period, the internal BRG register is clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed and is transferred to the UxBRGH and UxBRGL registers when complete. Note:

|