- Címlap

- LED kijelzők meghajtása

- Permetező projekt

- PIC18FxxK42

- PIC18FxxK42 I2C regiszterei

- PIC18FxxK42 órajel beállítása

- Pic18FxxK42 regiszterei

- Láb hozzárendelés PIC18FxxK42

- Pic18 I2C programozás

- PIC18FxxK42 I2C kommunikáció

- EEPROM memória használata

- LIN UART-tal fordítás

- LM75A és PIC18F45K42 I2C1 program

- Objektumok

- Pic18FxxK42 konfigurálás

- SPI

- UART PIC18(L)F45K42

- Watchdog Timer

- PIC18F45K42 timer2,-4,-6

- I2C modul 1

- PIC18F45K22 I2C lépései

- PIC18F45K42 USART regiszterei és azok magyarázata II.

- PIC18F45K42 USART regiszterei

- PIC18F45K42 timer1,-3,-5

- UART PIC18F45K42

- PIC18 utasításkészlete

- USART mudullal aszinkron kapcsolat két mikrokontroller közt

- CAN kommunikáció

- DS3231SN RTC

- Dell T 5600

- E-paper

- EGYÉB jegyzet

- ESP 8266 WiFi modul

- ESP-07 ESP-12x

- ESP-12F WiFi modul

- ESP32

- ESP8266

- Egyéb (elektronika)

- Emeléskijelző projekt

- Giroszkóp

- HASZNOSAK

- Hasznos általános linkek

- Illesztő modulok

- Kapcsolások, megoldások

- Kiszajú műveleti erősítő

- Konfigurálás

- LIN kommunikáció UART-tal

- MPASM PIC18

- Nyomásmérés MS5803-05BA-val

- Nyomásmérő I2C

- Nyomásszenzor SPD8xx I2C

- Nyák, nyáktervezés

- Operációs rendszerek

- PIC 18 mikrokontrollerek

- PIC18(L)F47K40

- PIC18(L)F65K40

- PIC18F45(K)50

- PIC18F87k22(80 láb)

- PROGRAMOZÁS

- Programozás

- Python 3

- RAUCH 2057153

- RDS

- RTC TLC 5947-el

- Rádiókapcsolat két mikrokontroller között

- Számítógépes programok

- TCS34725 színérzékelő

- TLC 5947

- TTP223 kapacitív nyomógomb

- USB + USB AN1310-el

- Ulefone Power 2

- Vektoros megszakítások

- Vetőgép

- Webfejlesztés

- WiFi, Bluetooth modulok

- Pickit 3 programozó

- Pic-Ethernet-Pic

- LM75A

- PWM CCPx modullal

- PWM PWMx modullal

- NCO

- TCS 3200 RGB érzékelés

- Nyáktervezés

- Oktatás

- PIC 24 mikrokontrollerek

PIC18FxxK42 I2C kommunikáció

PIC18FxxK42 I2C kommunikáció

I2C = Inter Integrated Circuit (Inter IC) picko_2kiad/RUP-106.pdf 170 oldaltól.

I2C kommunikáció (Eng.): Itt

Kijelzőre egy példa link: Itt

| - | <-- Mester hívja a szolgát és adatot küld a szolgának <-- Továbbiadatok küldése a szolgának <--- | - | ||||||||||||||||||||||||||

| A | - | Mester | Sz | Mester | Sz | Mester | .. | Mester | Sz | Me | - | |||||||||||||||||

| B | H | S | Mester megcímzi a szolgát és hívja | W | A | Adatok a mestertől | A | Adat... | .. | Adat... | A | P | H | |||||||||||||||

| C | - | 1 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 1 | 1 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 1 | 8 | 7 | ... | 2 | 1 | 1 | 1 | - |

| D | - | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | ... | x+1 | x+2 | x+3 | x+4 | x+5 |

| - | <-- Mester hívja a szolgát és adatot kér a szolgától <-- Továbbiadatok küldése a szolgától <--- | - | ||||||||||||||||||||||||||

| A | - | Mester | Sz | Szolga | Sz | Szolga | .. | Szolga | Mester | - | ||||||||||||||||||

| B | H | S | Mester megcímzi a szolgát és hívja | R | A | Adatok a Szolgától | A | Adat... | .. | Adat... | NA | P | H | |||||||||||||||

| C | - | 1 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 1 | 1 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 1 | 8 | 7 | ... | 2 | 1 | 1 | 1 | - |

| D | - | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | ... | x+1 | x+2 | x+3 | x+4 | x+5 |

Az adatot mindig az órajel magas periódusában viszgálja, ami lehet megas-, alacsony-, lefutó- (start jel), felfutó szintű. mester az, amelyik az órajelet szolgáltatja, a szolga pedig az, amelyik csak figyeli és felhasználja az órajelet.

S - Start jel. A startjel egy magas szintről alacsony szintre lefugró él az órajel magas szintű periódusában.

P - Stop jel, ami alacsony szintű jel és az órajelet szolgáltató (mester) szolgáltatja.

A - ACK jel,

NA - Fordította ACK jel. Fordított, mert ezt nem a szolga küldi visszajelzésként, hanem a mester

R - Adatok fogadása

W - Adatok küldése

MESTER KOMMUNIKÁCIÓJA

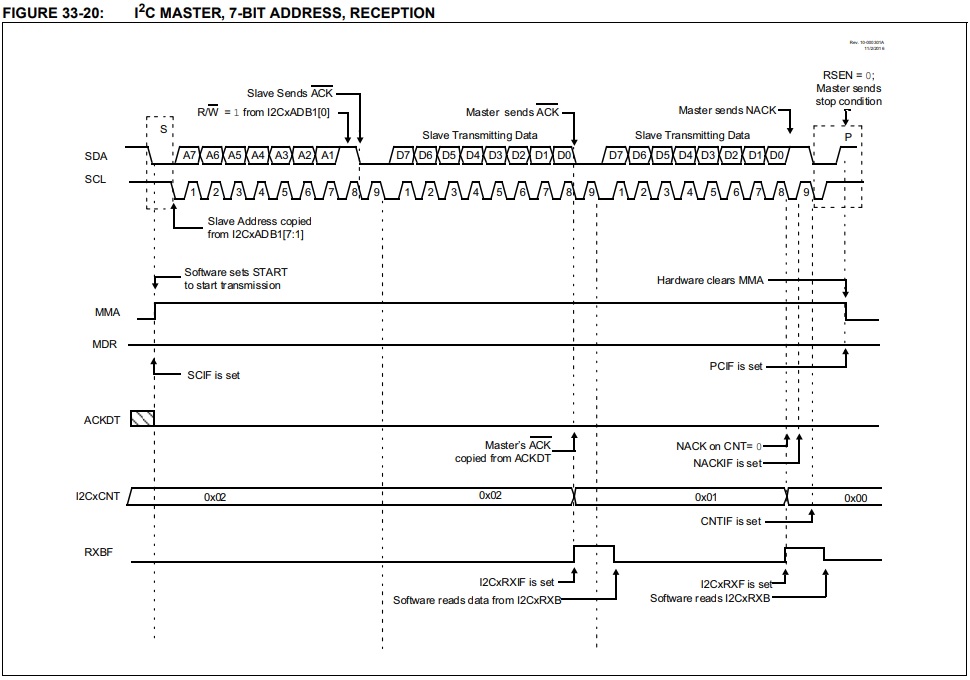

| A mester adatot kér, majd fogad a szolgától 7 bites címzéssel amit a szolga elküld. MASTER RECEPTION IN 7-BIT ADDRESSING MODE |

||

| Ez a szakasz leírja az I2C modul I2C-masterként konfigurált eseménysorozatait 7 bites címzési módban amikor adatokat küld a szolgának. A 33-20. ábrán vizuális láthatjuk mindazt ami a leírásban van. Mindez megtalálható a PIC18FxxK42 dokumentáció 569 oldalán. |

This section describes the sequence of events for the I2C module configured as an I2C master in 7-bit Addressing mode and is receiving data. Figure 33-20 is used as a visual reference for this description. | |

| 1. | A masterban szoftveresen be kell tölteni a szolga 7 bites <7:1> címét az I2CxADB1 regiszterbe, a <0> biten R/W-t kell megadni. R/W=0 ha adatot akarunk küldeni a szolgának (R/!W) R/W=1 ha adatot akaronk kérni a szolgától (R/!W) Meg kell még adni az I2CxCNT regiszterben, hogy hány bájt adatot akarunk küldeni vagy fogadni. Nullával kezdődik az érték, vagyis két bájt esetén 1-et kell megadni, a cím(adat) viszont nem számolható bele. |

Master software loads slave address in I2CxADB1 with R/W bit = d and number of bytes to be received in one sequence in I2CxCNT register. |

| 2. | A mester hardver vár az I2CxSTAT0 regiszter BFRE (<7>) bitjének az 1- re történő beállítására. A BFRE bit akkor 1, ha szabad az I2C kommunikációs busza, vagyis huzamosan magas szintre felhúzzák a felhúzó ellenállások. Ez után elinbítja a START jelet (lefutó él az adatvonalon, mígy a szinkronjel magas szinten van) kiküldi a shift regiszterből a címet és az R/W-t. Előbb a 7 bites cím magasabb helyiértékű bitjeit küldi ki, majd az R/W értákét, ami most 1. |

Master hardware waits for BFRE bit to be set; then shifts out start and address with R/W = 1. |

| 3. | Mester 9. órajel magas szintjére felengedi az adatvonalat, hogy a szolga nyugtázásként azt lehúzza, ami képezi az ACK jelet, jelezvén a mesternek, hogy felismerte a címet és kész küldeni a kért adatokat. (később adatküldéskor az adat megérkezését is így jelzi) folytatódhat a kommunikáció. |

Master sends out the 9th SCL pulse for ACK, master hardware clocks in ACK from Slave |

| 4. | Ha I2CxCON2 regiszter <4>, vagyis ABD = 0, akkor a címpufferek engedélyezve vannak. Ha a NACK, a mester hardver elküldi a stop-ot vagy beállítja az MDR-t (ha RSEN = 1), és várja a felhasználói szoftvert, hogy S bitet írjon újraindításhoz. Ha I2CxCON2 regiszter ABD = 1, akkor azaz a címpufferek le vannak tiltva. Ha a NACK, a mester hardver elküldi a Stop vagy az MDR beállítást (ha RSEN = 1), és várja a felhasználói szoftvert, hogy az új címet az I2CxTXB-be töltse be. Ebben az esetben figyelmen kívül kell hagyni az S bitre író szoftvert. ?????????????????????????????????????????? |

If ABD = 0; i.e., Address buffers are enabled If NACK, master hardware sends Stop or sets MDR (if RSEN = 1) and waits for user software to write to S bit for restart. If ABD = 1; i.e., Address buffers are disabled If NACK, master hardware sends Stop or sets MDR (if RSEN = 1) and waits for user software to load the new address into I2CxTXB. Software writes to the S bit are ignored in this case. |

| 5. | Ha az ACK, a master hardver 7 bites adatot kap a shift regiszterben. ??????????????????????????????????????????????? |

If ACK, master hardware receives 7-bits of data into the shift register. |

| 6. | Ha a mester adatfogadó buffere (tárolója) tele van, akkor ezt az I2CxSTAT1 regiszter RXBF bitje 1-re állással jelzi , a 7. szinkronjel leeső élenél megnyúlik az órajel. | If the receive buffer is full (i.e., RXBF = 1), clock is stretched on 7th falling SCL edge. |

| 7. | A mesternek ki kell olvasnia az előző adatokat az I2CxRXB-ből az RXBF törléséhez. | Master software must read previous data out of I2CxRXB to clear RXBF. |

| 8. | A master hardver 8. adatbitet megkapja a shift regiszterbe és ezt a mester áthelyezi az I2CxRXB tároló regiszterbe, minek hatására I2CxRXIF (PIR2<I2C1RXIF> vagy PIR5<I2C2RXIF>) és I2CxSTAT1<RXBF> bitek 1-re állnak be. Ekkor az I2CxCNT értéke is csökken 1-el. | Master hardware receives 8th bit of data into the shift register and loads it into I2CxRXB, sets I2CxRXIF and RXBF bits. I2CxCNT is decremented. |

| 9. | Ha I2CxCNT nem = 0, a master hardver az I2CxCON1<ACKDT>-ben megadott szintű ACK (nyugtázójel) jelet küld a szolgának. Ha I2CxCNT = 0, a master hardver az ACKCNT-t ACK értékként értékeli ki a slave-nek. A felhasználó feladata az ACKDT és az ACKCNT értékének helyes beállítása. Ha a felhasználó nem állítja az ACKCNT-et "1" -re, akkor a master hardver soha nem küld NACK-t, ha az I2CxCNT nulla lesz. Mivel a NACK nem látható a buszon, a mester hardver sem fogja megállítani a Stop állapotot. ????????????????? |

If I2CxCNT! = 0, master hardware clocks out ACKDT as ACK value to slave. If I2CxCNT = 0, master hardware clocks out ACKCNT as ACK value to slave. It is up to the user to set the values of ACKDT and ACKCNT correctly. If the user does not set ACKCNT to ‘1’, the master hardware will never send a NACK when I2CxCNT becomes zero. Since a NACK was not seen on the bus, the master hardware will also not assert a Stop condition. |

| 10. | Go to step 4. | |

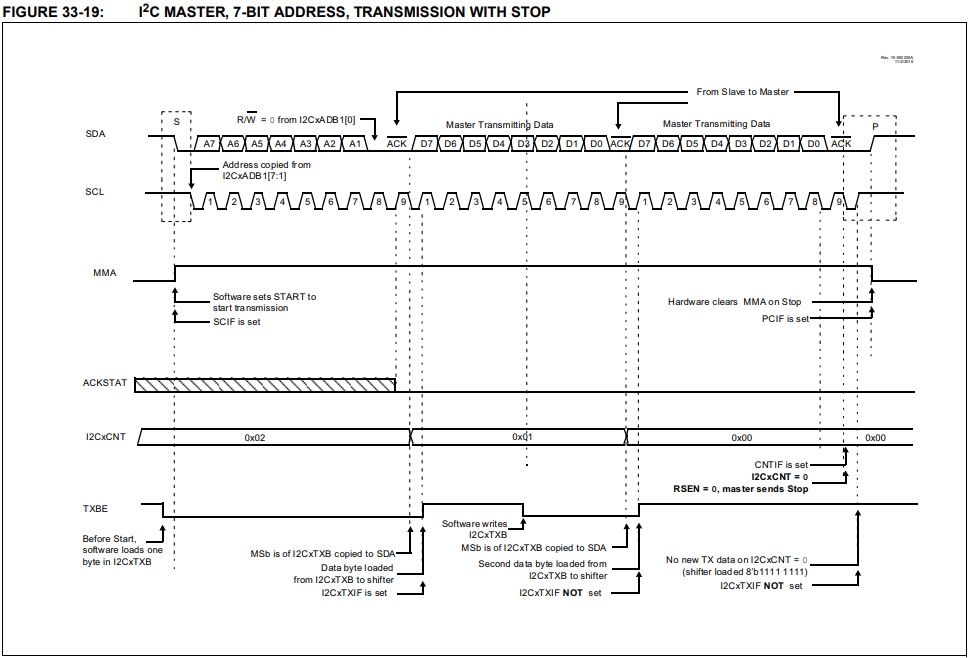

| A mester adatokat küld a szolgának 7 bites címzéssel MASTER TRANSMISSION IN 7-BITADDRESSING MODE |

||

| Ez a leírás bemutatja az I2C modul I2C-masterként konfigurált eseménysorozatait 7-bites címzési módban, és adatokat továbbít. A 33-19. ábra vizuális referenciaként szolgál erre a leírásra. A 33-19-es ábra vizuálisan is megmutatja mindezt. Mindez megtalálható a PIC18FxxK42 dokumentáció 567 oldalán. |

This section describes the sequence of events for the I2C module configured as an I2C master in 7-bit Addressing mode and is transmitting data. Figure 33-19 is used as a visual reference for this description. | |

| 1. | Ha I2CxCON2<ABD> = 0, tehát a címbufferek engedélyezve vannak, akkor a mesterprogram: 1, az átviendő bájtok számát betölti az I2CxCNT regiszterbe 2, a szolgacímet betölti a I2CxADB1 regiszterbe úgy hogy az írás/olvasás bitet 0-ra állítja(csak olvasható) 3, az első adatbájtot betölti az I2CxTXB regiszterbe A mesterprogram a Start (S) bit beállításával indíthatja el a kommunikáció folyamatát. Ha I2CxCON2<ABD> = 1; azaz a címpufferek le vannak tiltva, akkor a masterprogram 1, betölti az I2CxCNT-ben egy sorozatban továbbítandó bájtok számát 2, betölti a szolga címét és az R/W = 0 értékket az I2CxTXB regiszterbe 3,Az I2CxTXB-re írva a buszon elindul a kommunikáció és 1-re beáll az I2CxCON0<S> bit. Ebben az esetben figyelmen kívül haggya a szoftveresen beírt S bit értékét. |

If ABD = 0; i.e., Address buffers are enabled Master software loads number of bytes to be transmitted in one sequence in I2CxCNT, slave address in I2CxADB1 with R/W = 0 and the first byte of data in I2CxTXB. Master software has to set the Start (S) bit to initiate communication. If ABD = 1; i.e., Address buffers are disabled Master software loads the number of bytes to be transmitted in one sequence in I2CxCNT and the slave address with R/W = 0 into the I2CxTXB register. Writing to the I2CxTXB will assert the start condition on the bus and sets the S bit. Software writes to the S bit are ignored in this case. |

| 2. | A mester hardver vár a I2CxSTAT0<BFRE> bit 1-re állására (jelzi, hogy a busz szabad); majd a START jellel elindítja a kommunikációt, kiküldi a szolga címét (kezdve a magasabb helyiértékű felől) 7 biten, és 0. bitként utolsónak az R/!W jelet. | Master hardware waits for BFRE bit to be set; then shifts out start and address. |

| 3. | Ha az adatküldő tárolója kiürül (vagyis I2CxSTAT1<TXBE>=1) és I2CxCNT! = 0, akkor az I2CxTXIF* és az I2CxCON0<MDR> bitek 1-re állta be, és a 8. SCL lefutott. Az óra az I2CxTXB regiszterben az Ön által a következő adatok betöltésével tölthető be.?????? | If the transmit buffer is empty (i.e., TXBE = 1) and I2CxCNT!= 0, the I2CxTXIF and MDR bits are set and the clock is stretched on the 8th falling SCL edge. Clock can be started by loading the next data by te in I2CxTXB register. |

| 4. | A mester elküldi a 9. SCL impulzust a szolgának várva ACK jelre, vagyis a 9. órajel magas szintjén az SDA adatvonalat a mester felengedi, hogy a szolga nyugtázásként azt le tudja húzni, amit ACK jelnek hívunk | Master sends out the 9th SCL pulse for ACK. |

| 5. | Ha a mester a szolga ACK jelet fogadja solgától, az átviteli puffer (I2CxTXB) következő bájtja a shift regiszterbe töltődik, és ekkor az I2CxCNT regiszter értéke csökken 1-el. Megj.: Mi az I2CxTXB puffer regiszterbe írjuk be az elküldendő adatot. |

If the Master hardware receives ACK from Slave device, it loads the next byte from the transmit buffer (I2CxTXB) into the shift register and the value of I2CxCNT register is decremented. |

| 6. | Ha az elküldött adatra a szolga újból NACK jellel válaszol, akkor a mester kiadja a Stop vagy a RESTART jelet. | If a NACK was received, Master hardware asserts Stop or Restart |

| 7. | Eddig!!! Ha ABD = 0, akkor a címpufferek engedélyezettek: Ha I2CxCNT = 0, a mester hardver elküldi a stop-ot, vagy beállítja az MDR-t, ha az RSEN = 1, és várja a szoftvert, hogy újra beállítsa a Start bitet újraindítási feltétel kiadásához. Ha ABD = 1, akkor a címpufferek le vannak tiltva: Ha I2CxCNT = 0, a mester hardver elküldi a Stop vagy az MDR beállítást, ha RSEN = 1, és várja a szoftvert, hogy írja az új címet az I2CxTXB regiszterbe. Ebben az esetben figyelmen kívül kell hagyni az S bitre író szoftvert. |

If ABD = 0; i.e., Address buffers are enabled If I2CxCNT = 0, Master hardware sends Stop or sets MDR if RSEN = 1 and waits for the software to set the Start bit again to issue a restart condition. If ABD = 1; i.e., Address buffers are disabled If I2CxCNT = 0, Master hardware sends Stop or sets MDR if RSEN = 1 and waits for the software to write the new address to the I2CxTXB register. Software writes to the S bit are ignored in this case. |

| 8. | A mester hardverek adatokat szolgáltatnak az SDA-n. | Master hardware outputs data on SDA. |

| 9. | Ha TXBE = 1 és I2CxCNT! = 0, I2CxTXIF és MDR bitek vannak beállítva, és az óra feszül a 8. alá tartozó SCL szélén. A felhasználó felszabadíthatja az órát a következő adatbájt I2CxTXB regiszterbe írásával. | If TXBE = 1 and I2CxCNT! = 0, I2CxTXIF and MDR bits are set and the clock is stretched on 8th falling SCL edge. The user can release the clock by writing the next data byte to I2CxTXB register. |

| 10. | A master slave órákat az ACK-ból a slave-ből, és betölti a következő adatbájtot az I2CTXB-ből a shift regiszterbe. Az I2CxCNT értéke csökken. | Master hardware clocks in ACK from Slave, and loads the next data byte from I2CTXB to the shift register. The value of I2CxCNT is decremented. |

| 11. | Folytatás a 7. lépéssel. | Go to step 7. |

SZOLGA KOMMUNIKÁCIÓJA

| A mester adatot kér a szolgétól 7 bites címzéssel amit a szolga elküld. | ||

| Ebben a lépéssorozatonkénti leírásban az I2C kommunikációt ismerhetjük meg oly móüdon, hogy a mester küld adatokat a szolgának mégpesdig 7 bites címzéses megoldásban. A 33-9 és a 33-10-es ábra vizuálisan is megmutatja mindezt. Mindez megtalálható a PIC18FxxK42 dokumentáció 556 oldalán. |

This section describes the sequence of events for the I2C module configured as an I2C slave in 7-bit Addressing mode and is transmitting data. Figure 33-9 and Figure 33-10 are used as a visual reference for this description. |

|

| 1. | A mester a START jellel indítja el a kommunikációt: A mester az adat vonalon (SDA) a felhúzó ellenállások által pozitív feszültséget a nyitott kollektoros kimenetével lehúzza, míg ilyenkor hasonló módon az órajel is pozitív feszültségen van. Ilyenkor még nincs órajel az SCL vonalon, fenn van magas szinten és a startjel idején is fenn van. Tehát az SDA vonalon a lefutó él lesz a START jel. Tehát a startjel (mindig) egy magasról alacsonyra lefutó él. Az szinkronjel a START jel után indul csak el mégpedig magas szintről kezdve. Az indítási állapotban megszakítást jelző <0>. bit I2CxPIR regiszterben vagyis az I2CxPIR<SCIF> megszaításjelző bit magas szintre áll be. A fenti folyamat RESTART esetén is érvényes. Restartr az, amikor a mester adatot küld és nem szabadítja fel a SDA, SCL vonalat STOP jellet, ami szintén egy él az órajel magas zsintű periódusa latt, csak ez egy felfutó él. Megj.: tényleges megszakítás csak akkor valósul meg, ha az engedélyezve van de az SCIF jelez.. |

Master asserts Start condition (can also be a restart) on the bus. Start condition Interrupt Flag (SCIF) in I2CxPIR register is set. |

| 2. | Ha a START jel alatt ewngedélyezve van Az SCIE bit (I2CxPIE<SCIE>=1), akkor PIRx<I2CxIF> jelzőbit 1-re állásaával jelzi a SART jel meglétét. | If Start condition interrupt is enabled (SCIE bit is set), generic interrupt I2CxIF is set. |

| 3. | A mester 8 bitet küld az adatbuszra, <7:1> biten a címet és a <0>. biten R /! W jelet, ami most 1 lesz. A <0> biten az 1 jelzi, hogy adatokat fog kérni a szolgától. A küldés illetve fogadás az idő függvényében a magasabb helyiértékű bitek felől halad az alacsonyabb felé. | Master transmits eight bits – 7-bit address and R/!W = 1 |

| 4. | A beérkezett címet a szolga összehasonlítja az I2CxADR0 / I2CxADR1 / I2CxADR2 / I2CxADR3 regiszterek valamelyikével. A címről annyit, hogy a négy magasabb helyiértékű bit tartalmazza a típuscímet. A tipuscím gyárilag van beállítva, attól függ az étrékre, hogy az milyen a hardver. Pld eeprom esetében a tipuscím hexa(A)= Bináris(1010). A másik 3 bit pedig a hardver cím. A hardver cím 3 bitjét többnyire a szolga eszköz megfelelő lábainak + vagy 0V-ra kapcsolásával lehet megadni. Lásd a 33.4.1 "Szolga címzési módok" című fejezetet a szolga címzés üzemmódoknál. |

Received address is compared with the values in I2CxADR0/I2CxADR1/I2CxADR2/I2CxADR3 registers. Refer to Section 33.4.1 “Slave Addressing Modes” for Slave Addressing modes |

| 5. | Ha a szolga megállapítja, hogy őt címezte meg a mester, vagyis megegyezik az ő címével, akkor az I2CxSTAT0 regiszterben az SMA bit 1-re vált (I2CxSTAT0<SMA>=1). A címmel érkező (R/!W) <0>. bit is kiértékelésre kerül. A mestertől a <7:1> bien a címzés és a <0>. biten érkezett jelsorozatból az R/!W bit átmásolódik a szolga R/!W bit tárolójába, jelen estben 1 kerül bele. Ez aztán kiértékelésre kerül, vagyis jelzi a szolgának, hogy a szolgától adatot kér a mester. Ez a valóságban a jelen beállításban a szolga I2CxADB0 regiszterébe kerül mégpesig úgy, hogy a címadatok <ADB7:ADB1> (<7:1>)-be, az R/!W bit pedig az I2CxADB0<ADB0>(<0> bit)-be kerül. Ha a cím nem egyezik meg, akkor a modul üresjáratban marad. |

If address matches; SMA in I2CxSTAT0 register is set, R/W is copied to R/W bit, D/A bit is cleared. If the address does not match; module becomes idle. |

| 6. | Tehát az illeszkedő (megegyező) címadatok a szolga I2CxADB0<1-7> regiszterébe töltődnek be, minek a hatására a szolga I2CxPIR regiszterében ADRIF bit magas szintre áll be. | The matched address data is loaded into I2CxADB0 and ADRIF in I2CxPIR register is set. |

| 7. | Ha a szolgánál engedélyezve van a megszakítás amikor megérkezik a cím, az I2CxPIE<ADRIE>(<3>)=1-el, akkor engedályezve van az I2CxCON1<CSTR>(<4>) is. Ilyenkor a szolga programja képes olvasni az I2CxADB0 címet, és az SCL felszabadítása előtt beállítani / törölni az ACKDT-t. Az SCL vonal felszabadulhat a CSTR törlésével. Ha I2CxCON0<CSTR>=1, akkor a mester hosszabb ideig lent tartja az órajel, vagyis elnyújtja, hogy a szolgának legyen ideje értékelni a vett jeleket, majd kiadni a nyugtázó (ACK) jelet. Az SCL vonal felszabadulhat a CSTR törlésével, amikor is kiadja majd a szolga az ACK jelet. |

If Address hold interrupt is enabled (ADRIE = 1), CSTR is set. I2CxIF is set. Slave software can read address from I2CxADB0 and set/clear ACKDT before releasing SCL. SCL line can be released by clearing CSTR. |

| 8. | ?- Ha az átviteli puffer üres az előző tranzakcióból, azaz TXBE = 1 és I2CxCNT! = 0 (I2CxTXIF = 1), a CSTR be van állítva. A slave szoftvernek be kell töltenie az adatokat az I2CxTXB-be, hogy kiadja az SCL-t. I2CxCNT csökkenés után a byte be van töltve a shift regiszterbe. | If the transmit buffer is empty from the previous transaction, i.e. TXBE=1 and I2CxCNT!=0 (I2CxTXIF =1), CSTR is set. Slave software must load data into I2CxTXB to release SCL. I2CxCNT decrements after the byte is loaded into the shift register. |

| 9. | A szolga vár a 9. óraimpulzusban arra, hogy a mester felengedje az adatvonalat, amire a szolga ACK jelet kiadja a mesternek, jelezvén, hogy megérkezett az adat. | Slave hardware waits for 9th SCL pulse with ACK data from Master. |

| 10. | Ha az I2CxCNT = 0, akkor az I2CxPIR regiszter CNTIF (megszakításjelző bit talán) 1-re áll be. | If I2CxCNT=0, CNTIF is set. |

| 11. | ?- Ha a Megerősítés megszakítása és tartása engedélyezve van (I2CxPIE<ACKTIE> = 1), akkor a CSTR be van állítva, az I2CxIF be van állítva. | If the Acknowledge interrupt and hold is enabled (ACKTIE=1), CSTR is set, I2CxIF is set. |

| 10. | ?- Az Slave szoftver megváltoztathatja az I2CxCON1<ACKDT> értékét, mielőtt elengedi az SCL-t a CSTR törlésével. mielőtt az órajel lefut. | Slave software can change the value of ACKDT before releasing SCL by clearing CSTR. |

| 13. | ,- A mester nyolc SCL (órajel) impulzust küld az adatok (következő adat) időzítéséhez, vagy a tranzakció befejezéséhez kiadja a Stop jelet, ami egy fent/le él.. | Master sends eight SCL pulses to clock out data or asserts a Stop condition to end the transaction. |

| 14. | Folytassa a 8. lépéssel. | Go to step 8. |

-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

| I2C módban a mester adatfogadása a szolgától 7 bites címzéssel | ||

| ?- A mester által továbbított címsávban lévő 8. bitet használják annak meghatározására, hogy a mester szeretne olvasni a Slave dev ice-ből vagy írni. Ha be van állítva, azt jelöli, hogy a mester a slave-ről akar olvasni, és ha törölni akarja, azt jelenti, hogy a mester a slave eszközre akar írni. Ha van egy címegyezés, az R / W bit átmásolódik az I2CxSTAT0 regiszter R / W bitjére. ?-Ez a leírás ismerteti az I2C modul konfigurálását I2C 7-bites címzési módban konfigurált eseménysorozatait, és adatokat fogad. 33-6. Ábra, 33-7. Ábra és 33-8. Ábra vizuális referenciaként szolgál erre a leírásra |

Katalógus 552 oldal. SLAVE OPERATION IN 7-BIT ADDRESSING MODE The 8th bit in an address byte transmitted by the master is used to determine if the Master wants to read from or write to the Slave dev ice. If set, it denotes that the Master wants to read from the slave and if cleared it means the master wants to write to the slave device. If there is an address match, the R/W bit is copied to the R/W bit of the I2CxSTAT0 register. This section describes the sequence of events for the I2C module configured as an I2C slave in 7-bit Addressing mode and is receiving data. Figure 33-6, Figure 33-7, and Figure 33-8 are used as a visual reference for this description. |

|

| 1. | ?-A mester a buszon elindítja a start állapotot (lehet újraindítás is). Az indítási állapot Megszakítási zászló (SCIF) van beállítva az I2CxPIR regiszterben. | Master asserts Start condition (can also be a restart) on the bus. Start condition Interrupt Flag (SCIF) in I2CxPIR register is set. |

| 2. | ?- Ha az indítási állapot megszakítása engedélyezett (SCIE bit beállítása), az általános megszakítás I2CxIF beállításra kerül. | If Start condition interrupt is enabled (SCIE bit is set), generic interrupt I2CxIF is set. |

| 3. | ?-A mester nyolc bitet küld - 7 bites címet és R / W = 0. | Master transmits eight bits – 7-bit address and R/W=0. |

| 4. | ?-A beérkezett címet összehasonlítjuk az I2CxADR0 / I2CxADR1 / I2CxADR2 / I2CxADR3 regiszterek értékeivel. A slave címzési módokról lásd a 33.4.1 szakasz "Slave Addressing Mode" című részét. | Received address is compared with the values in I2CxADR0/I2CxADR1/I2CxADR2/I2CxADR3 registers. Refer to section Section 33.4.1 “Slave Addressing Modes”for slave addressing modes. |

| 5. | ?-Ha a cím megegyezik; SMA az I2CxSTAT0 regiszterben van beállítva, az R / W át lett másolva R / W bitre, a D / A bit törlődik. Ha a cím nem egyezik meg; a modul üresjáratban marad. | If address matches; SMA in I2CxSTAT0 register is set, R/W is copied to R/W bit, D/A bit is cleared. If the address does not match; module becomes idle. |

| 6. | ?-Az illesztett címadatokat I2CxADB0-ba töltik be, és I2CxPIR regiszterben ADRIF be van állítva. | The matched address data is loaded into I2CxADB0 and ADRIF in I2CxPIR register is set. |

| 7. | ?-Ha a Címtartás megszakítás engedélyezve van (ADRIE = 1), a CSTR be van állítva. I2CxIF van beállítva. A slave szoftver képes olvasni az I2CxADB0 címet, és az SCL felszabadítása előtt beállítani / törölni az ACKDT-t. | If Address hold interrupt is enabled (ADRIE=1), CSTR is set. I2CxIF is set. Slave software can read address from I2CxADB0 and set/clear ACKDT before releasing SCL. |

| 8. | ?- Ha vannak korábbi hibaállapotok, például a Receive buffer overflow vagy az átviteli buffer aluláteresztő hibái, akkor a slave egy NACK-ot kényszerít és a modul üresjáratba kerül. | If there are any previous error conditions, e.g., Receive buffer overflow or transmit buffer under- flow errors, Slave will force a NACK and the module becomes idle. |

| 9. | ?- Az ACKDT értéket SDA-ra másolja az ACK impulzusra, hogy a Mester a 9. SCL impulzuson leolvassa. | ACKDT value is copied out to SDA for ACK pulse to be read by the Master on the 9th SCL pulse. |

| 10. | Ha a nyugtázó szakítani, és tartsa be van kapcsolva (ACKTIE = 1), CSTR van beállítva, I2CxIF van beállítva, akkor Slave program tudja olvasni címet I2CxADB0 regisztrálni és módosítsa az értéket a ACKDT kiadása előtt SCL törlésével CSTR. | If the Acknowledge interrupt and hold is enabled (ACKTIE=1), CSTR is set, I2CxIF is set, then Slave software can read address from I2CxADB0 register and change the value of ACKDT before releasing SCL by clearing CSTR. |

| 11. | A mester az adatbájt első hét SCL impulzusát vagy a Stop állapotot (NACK esetén) küldi. | Master sends first seven SCL pulses of the data byte or a Stop condition (in the case of NACK). |

| 10. | Ha Stop állapot; PCIF I2CxPIR regiszterben van beállítva, a modul készenléti állapotba kerül. | If Stop condition; PCIF in I2CxPIR register is set, module becomes idle. |

| 13. | Ha a vételi puffer tele van az előző tranzakciótól, azaz RXBF = 1 (I2CxRXIF = 1), a CSTR be van állítva. A slave szoftvernek ki kell olvasnia az I2CxRXB-ből származó adatokat a kommunikáció folytatásához. | If the receive buffer is full from the previous transaction i.e. RXBF=1 (I2CxRXIF=1), CSTR is set. Slave software must read data out of I2CxRXB to resume communication. |

| 14. | A mester az adatbájt 8. SCL impulzusát küldi. D / A bit be van állítva, a WRIF be van állítva. | Master sends 8th SCL pulse of the data byte. D/A bit is set, WRIF is set. |

| 15. | Az I2CxRXB új adatokat tölt be, az RXBF bit be van állítva, az I2CxRXIF be van állítva. | I2CxRXB is loaded with new data, RXBF bit is set, I2CxRXIF is set. |

| 16. | Ha az Adat megírása megszakítás és a tartás engedélyezve van (WRIE = 1), a CSTR be van állítva, az I2CxIF be van állítva. Az Slave szoftver az I2CxRXB-ről és az ACKDT beállításáról / törléséről olvasható az SCL felszabadítása előtt a CSTR törlésével. | If Data write interrupt and hold is enabled (WRIE=1), CSTR is set, I2CxIF is set. Slave software can read data from I2CxRXB and set/clear ACKDT before releasing SCL by clearing CSTR. |

| 17. | Ha I2CxCNT = 0, akkor az ACKCNT érték az SDA-ba kerül; Egyébként, ha I2CxCNT! = 0, az ACKDT értéket használják, és az I2CxCNT értéke csökken. | If I2CxCNT=0, the ACKCNT value is output to the SDA; else, if I2CxCNT!=0, the ACKDT value is used and the value of I2CxCNT is decremented. |

| 18. | Az ACK értéket SDA-ba másolja, hogy a Mester a 9. SCL impulzuson leolvassa. | The ACK value is copied out to SDA to be read by the Master on the 9th SCL pulse. |

| 19. | Ha I2CxCNT = 0, a CNTIF be van állítva. | If I2CxCNT=0, CNTIF is set. |

| 20. | Ha egy NACK-t küldtek, a NACKIF be van állítva, a modul üresjáratban marad. | If a NACK was sent, NACKIF is set, module becomes idle. |

| 21. | Ha ACKTIE = 1, CSTR van beállítva, I2CxIF van beállítva. A slave szoftver az I2CxRXB clearing RXBF-ből származó adatokat képes olvasni, mielőtt az SCL-t felszabadítaná a CSTR törlésével. | If ACKTIE=1, CSTR is set, I2CxIF is set. Slave software can read data from I2CxRXB clearing RXBF, before releasing SCL by clearing CSTR. |

| 22. | Folytassa a 11. lépéssel. | Go to step 11. |

Az adatbiteket az adó, az ACK bitet a vevő küldi. Ha a vevő nem képes adatot venni – mert egyéb feladatokat lát el –, akkor ezt két módon jelezheti:

- Nem küld nyugtázást (ACK bitet) a bájt végén. Ilyenkor a mester azonnal megszakítja az adatforgalmat, és később újra próbálkozik, természetesen egy újabb START feltétellel kezdve.

- Alacsony szinten tartja az SCL vonalat, ezt megteheti akár egy bájt vételének a „kellős közepén” is. Ilyenkor a mester megvárja, míg a szolga „elereszti” az SCL vonalat, és ott folytatja, ahol az adatforgalom félbeszakadt. Fontos kiemelni, hogy az adat- és az órajelvonalat az adó és a vevő felváltva használja. Ez megköveteli mind az adó, mind a vevő számára a nagyon pontos kommunikációs feltételek betartását. A „minden bájt nyugtázása” szabály alól két kivétel van:

- Az egyik akkor lép fel, ha a mester a vevő (MST/RCV). Ilyenkor jelezni kell az adatbájtsorozat végét, a küldőnek nem adva ACK-ot. Az ACK jelhez kapcsolódó órajelet a mester természetesen generálja, de az SDA vonalat nem húzza le L szintre. Ezt hívják negatív nyugtázásnak (NACK).

- A másik kivétel: a szolga akkor küld NACK jelet, ha nem képes újabb adatbájtokat elfogadni. Ez akkor lép fel, ha olyan átvitelt kezdeményezünk, amit nem képes fogadni.

Adatforgalom a buszon: A buszon lévő minden eszköznek saját címe van. Mielőtt adatátvitel történne a buszon, a mester START állapotba hozza a buszt, majd kiadja a buszra a szolga címét, amelyikkel adatot akar cserélni. Az a szolga, amelyik felismeri a saját címét, ACK jelet küld vissza. A címzést a mester végzi közvetlenül START állapot után. Ez az első küldött bájt.

A cím hétbites. A nyolcadik bit dönti el a szolgával történő adatcsere irányát. 0 bit jelöli az írást, ilyenkor a mester küld adatokat (W), 1 értékű bit pedig az olvasást (R).

A buszra kapcsolódó eszközök címei két kategóriába sorolhatók: az egyik kategóriában a cím programozható, ezek általában a mikrokontrollerek. A másik kategóriát a különféle funkciókat megvalósító perifériaáramkörök alkotják.

Ezeknél az eszközök címe két részből tevődik össze: egy típuscímből (4 bit) és egy hardvercímből (3 bit); az eszköz tokozásán a megfelelő lábak 0-ba, illetve 1-be kötésével. A típuscím az azonos (típusú) tokoknál mindig megegyezik.

Ezzel a címmel jelentkezik be a slave eszköz, illetve ezzel a címmel szólítja meg a master eszköz a slave-et adatcsere előtt (például az EEPROMoknál a típuscím 0AH [1010]).

Az egy mester – több szolga struktúrájú buszon zajló adatátvitel az ábrán látható (M jelöli a mester, Sz a szolga által küldött adatbiteket).

Master Write: A mester START állapotba hozza a buszt (S) és kiküldi a szolga címét. A cím legkisebb helyi értékű bitje W=0. Ezt a szolga az ACK jel visszaküldésével igazolja (A). Ezek után a mester küldi az adatokat a szolgának (DATA), és az minden bájt vételét (A) küldésével igazolja. Az utolsó adat küldése után a mester STOP állapotba hozza a buszt (P).

Master Read: A mester START állapotba hozza a buszt (S) és kiküldi a szolga címét. A cím legkisebb helyi értékű bitje R=1. Ezt a szolga az ACK jel visszaküldésével igazolja (A). Ezek után a mester fogadja az adatokat a szolgától (DATA= Adat), és minden bájt vételét (A) küldésével igazolja. Az utolsó adat küldését a mester negatív nyugtázással jelzi (NA). Ezek után a mester STOP állapotba hozza a buszt (P).

A fenti esetben a mester minden átvitelnél újból nyitja és zárja a buszt. Amennyiben a buszon a mester több szolgával akar adatot cserélni, a minden átvitelt lezáró STOP, majd az indító újabb START állapot sokat lassít az átvitelen. Ilyenkor használható az ismételt START állapot generálása. Ez az jelenti, hogy az átviteleket nem STOP (P), hanem a következőt indító START (S) állapottal fejezzük be, azaz a mester a buszt folyamatosan használja.

Ismételt START állapot használata: Itt egy olyan eset látható, amikor először a mester adatokat kapott egy szolgától, majd adatokat küld a nem szükségképpen azonos című szolgának. Az adatátviteli protokollokat két módon lehet megvalósítani: beépített hardver segítségével (ilyeneket tartalmaznak az erre felkészített mikrokontrollerek és az I2C buszra kifejlesztett periféria-áramkörök), vagy megvalósítására „bit-billegtetéses” programot írhatunk.

• •

• •