- Címlap

- LED kijelzők meghajtása

- Permetező projekt

- PIC18FxxK42

- PIC18FxxK42 I2C regiszterei

- PIC18FxxK42 órajel beállítása

- Pic18FxxK42 regiszterei

- Láb hozzárendelés PIC18FxxK42

- Pic18 I2C programozás

- PIC18FxxK42 I2C kommunikáció

- EEPROM memória használata

- LIN UART-tal fordítás

- LM75A és PIC18F45K42 I2C1 program

- Objektumok

- Pic18FxxK42 konfigurálás

- SPI

- UART PIC18(L)F45K42

- Watchdog Timer

- PIC18F45K42 timer2,-4,-6

- I2C modul 1

- PIC18F45K22 I2C lépései

- PIC18F45K42 USART regiszterei és azok magyarázata II.

- PIC18F45K42 USART regiszterei

- PIC18F45K42 timer1,-3,-5

- UART PIC18F45K42

- PIC18 utasításkészlete

- USART mudullal aszinkron kapcsolat két mikrokontroller közt

- CAN kommunikáció

- DS3231SN RTC

- Dell T 5600

- E-paper

- EGYÉB jegyzet

- ESP 8266 WiFi modul

- ESP-07 ESP-12x

- ESP-12F WiFi modul

- ESP32

- ESP8266

- Egyéb (elektronika)

- Emeléskijelző projekt

- Giroszkóp

- HASZNOSAK

- Hasznos általános linkek

- Illesztő modulok

- Kapcsolások, megoldások

- Kiszajú műveleti erősítő

- Konfigurálás

- LIN kommunikáció UART-tal

- MPASM PIC18

- Nyomásmérés MS5803-05BA-val

- Nyomásmérő I2C

- Nyomásszenzor SPD8xx I2C

- Nyák, nyáktervezés

- Operációs rendszerek

- PIC 18 mikrokontrollerek

- PIC18(L)F47K40

- PIC18(L)F65K40

- PIC18F45(K)50

- PIC18F87k22(80 láb)

- PROGRAMOZÁS

- Programozás

- Python 3

- RAUCH 2057153

- RDS

- RTC TLC 5947-el

- Rádiókapcsolat két mikrokontroller között

- Számítógépes programok

- TCS34725 színérzékelő

- TLC 5947

- TTP223 kapacitív nyomógomb

- USB + USB AN1310-el

- Ulefone Power 2

- Vektoros megszakítások

- Vetőgép

- Webfejlesztés

- WiFi, Bluetooth modulok

- Pickit 3 programozó

- Pic-Ethernet-Pic

- LM75A

- PWM CCPx modullal

- PWM PWMx modullal

- NCO

- TCS 3200 RGB érzékelés

- Nyáktervezés

- Oktatás

- PIC 24 mikrokontrollerek

PIC18FxxK42 órajel beállítása

Adatlap (pdf): PIC18F(L)xxK42.pdf

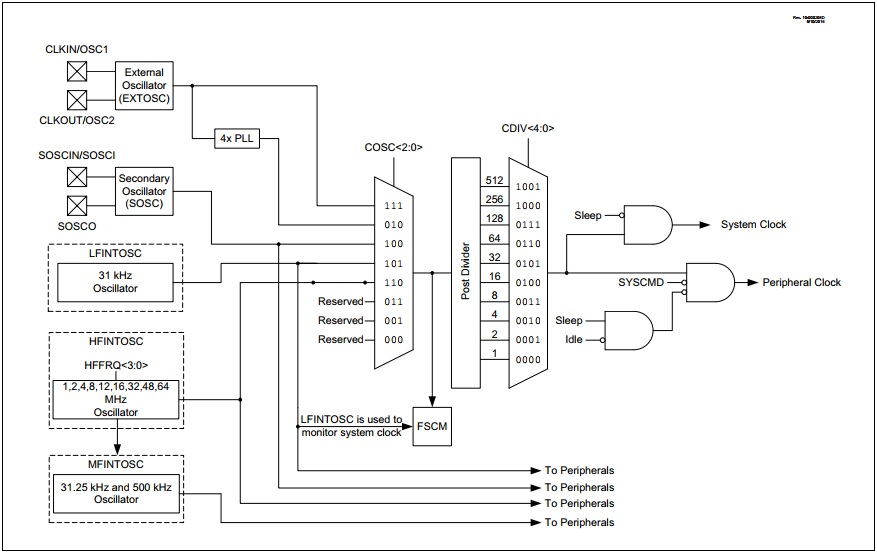

Katalógos 93. oldal:

Hiba a rajzon, hogy a CDIV<4:0> helyesen CDIV<3:0>

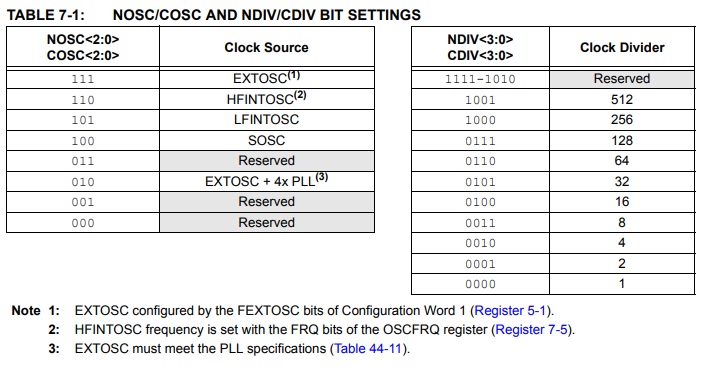

OSCCON1<3:0> = NDIV<3:0> (Írható, olvasható. Reset esetén a konfigurációtól függóen felülbírálódik)

OSCCON1<6:4> = NOSC<2:0> (Írható, olvasható. Reset esetén a konfigurációtól függóen felülbírálódik)

OSCCON1<7> = Nem használt

OSCCON2<3:0> = CDIV<3:0> (Csak olvasható)

OSCCON2<6:4> = COSC<2:0> (Csak olvasható)

OSCCON2<7> = Nem használt

Azalábbi ködok hasznosak lehetnek programírásnál:

Főprogram forráskódja :

LIST P=PIC18F45K42 ; ISO 8859-2

#include p18f45k42.inc ;

valtozok: UDATA_ACS ; H'10' ; nincs kezdo memoriacim megadva ';' végett az ACCESS ramban

W_TEMP RES 1 ; w register for context saving (ACCESS)

STATUS_TEMP RES 1 ; status used for context saving

BSR_TEMP RES 1 ; bank select used for ISR context saving

global konfig_ ;

extern konfig ;

ORG 0X0000

CODE

; FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF

goto konfig ;

konfig_:

goto orajel_teszt

goto $ ;

; FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF

orajel_teszt: ; A 40/23-AS LÁBON MEG LEHET MÉRNI A FREKVENCIÁT, AMINEK

; A 24 SZERESE LESZ A CPU ÓRAJELÉNEK A FREKVENCIÁJA

banksel ANSELC ;

bcf ANSELC,ANSELC4 ; Digitális legyen a (40/23) 23-as láb

banksel TRISC

bcf TRISC,TRISC4 ; Kimenet legyen a 23-as láb

; Próba oszcilloszkóppal vagy frekvenciamérővel vizsgálva:

banksel LATC

; Egy félperiódushoz 12 CPU óraimpulzus kell, így a:

; CPU órajel (Hz) = 24 X Kimeneti frekvencia (Hz)

btg LATC,LATC4 ; Átvált a kimenet. 1 ciklusú utasítás (4 órajel)

goto $-2 ; 2 ciklosú utasítás (8 órajel)

; fenti két soron marad a programfutás

END

Konfigurációs fájl forráskódja (részben konfigurált):

; External Oscillator Selection:

; FEXTOSC = LP LP (crystal oscillator) optimized for 32.768 kHz; PFM set to low power

; FEXTOSC = XT XT (crystal oscillator) above 100 kHz, below 8 MHz; PFM set to medium power

; FEXTOSC = HS HS (crystal oscillator) above 8 MHz; PFM set to high power

; FEXTOSC = RESERVED Reserved (DO NOT USE)

CONFIG FEXTOSC = OFF ; Oscillator not enabled

; FEXTOSC = ECL EC (external clock) below 100 kHz; PFM set to low power

; CONFIG FEXTOSC = ECM ; EC (external clock) for 500 kHz to 8 MHz; PFM set to medium power

; CONFIG FEXTOSC = ECH ; EC (external clock) above 8 MHz; PFM set to high power

;

; Reset Oscillator Selection:

; RSTOSC = HFINTOSC_64MHZHFINTOSC with HFFRQ = 64 MHz and CDIV = 1:1

; RSTOSC = RESERVED_1 Reserved

; RSTOSC = EXTOSC_4PLL EXTOSC with 4x PLL, with EXTOSC operating per FEXTOSC bits

; RSTOSC = RESERVED_2 Reserved

; RSTOSC = SOSC Secondary Oscillator

; RSTOSC = LFINTOSC Low-Frequency Oscillator

; CONFIG RSTOSC = HFINTOSC_1MHZHFINTOSC ; with HFFRQ = 4 MHz and CDIV = 4:1

; RSTOSC = EXTOSC EXTOSC operating per FEXTOSC bits (device manufacturing default)

;

; Clock out Enable bit:

; CLKOUTEN = ON CLKOUT function is enabled

; CLKOUTEN = OFF CLKOUT function is disabled

;

; PRLOCKED One-Way Set Enable bit:

; PR1WAY = OFF PRLOCK bit can be set and cleared repeatedly

; CONFIG PR1WAY = ON ; PRLOCK bit can be cleared and set only once

;

; Clock Switch Enable bit:

; CSWEN = OFF The NOSC and NDIV bits cannot be changed by user software

; CSWEN = ON Writing to NOSC and NDIV is allowed

;

; Fail-Safe Clock Monitor Enable bit:

; FCMEN = OFF Fail-Safe Clock Monitor disabled

; FCMEN = ON Fail-Safe Clock Monitor enabled

;

; MCLR Enable bit:

; CONFIG MCLRE = INTMCLR ; If LVP = 0, MCLR pin function is port defined function; If LVP =1, RE3 pin fuction is MCLR

; MCLRE = EXTMCLR If LVP = 0, MCLR pin is MCLR; If LVP = 1, RE3 pin function is MCLR

;

; Power-up timer selection bits:

; PWRTS = PWRT_1 PWRT set at 1ms

; PWRTS = PWRT_16 PWRT set at 16ms

; PWRTS = PWRT_64 PWRT set at 64ms

; PWRTS = PWRT_OFF PWRT is disabled

;

; Multi-vector enable bit:

; CONFIG MVECEN = OFF ; Interrupt contoller does not use vector table to prioritze interrupts

; MVECEN = ON Multi-vector enabled, Vector table used for interrupts

;

; IVTLOCK bit One-way set enable bit:

; IVT1WAY = OFF IVTLOCK bit can be cleared and set repeatedly

; CONFIG IVT1WAY = ON ; IVTLOCK bit can be cleared and set only once

;

; Low Power BOR Enable bit:

; LPBOREN = ON ULPBOR enabled

CONFIG LPBOREN = OFF ; ULPBOR disabled

;

; Brown-out Reset Enable bits:

; BOREN = OFF Brown-out Reset disabled

; BOREN = ON Brown-out Reset enabled according to SBOREN

; BOREN = NOSLP Brown-out Reset enabled while running, disabled in Sleep; SBOREN is ignored

; BOREN = SBORDIS Brown-out Reset enabled , SBOREN bit is ignored

;

; Brown-out Reset Voltage Selection bits:

; BORV = VBOR_2P85 Brown-out Reset Voltage (VBOR) set to 2.8V

; BORV = VBOR_2P7 Brown-out Reset Voltage (VBOR) set to 2.7V

; BORV = VBOR_245 Brown-out Reset Voltage (VBOR) set to 2.45V

; BORV = VBOR_190 Brown-out Reset Voltage (VBOR) set to 1.90V

;

; ZCD Disable bit:

; ZCD = ON ZCD always enabled

; ZCD = OFF ZCD disabled. ZCD can be enabled by setting the ZCDSEN bit of ZCDCON

;

; PPSLOCK bit One-Way Set Enable bit:

CONFIG PPS1WAY = OFF ; PPSLOCK bit can be set and cleared repeatedly (subject to the unlock sequence)

; CONFIG PPS1WAY = ON ; PPSLOCK bit can be cleared and set only once; PPS registers remain locked after one clear/set cycle

;

; Stack Full/Underflow Reset Enable bit:

; STVREN = OFF Stack full/underflow will not cause Reset

CONFIG STVREN = ON ; Stack full/underflow will cause Reset

;

; Debugger Enable bit:

; DEBUG = ON Background debugger enabled

; DEBUG = OFF Background debugger disabled

;

; Extended Instruction Set Enable bit:

; XINST = ON Extended Instruction Set and Indexed Addressing Mode enabled

CONFIG XINST = OFF ; Extended Instruction Set and Indexed Addressing Mode disabled

;

; WDT Period selection bits:

; WDTCPS = WDTCPS_0 Divider ratio 1:32

; WDTCPS = WDTCPS_1 Divider ratio 1:64

; WDTCPS = WDTCPS_2 Divider ratio 1:128

; WDTCPS = WDTCPS_3 Divider ratio 1:256

; WDTCPS = WDTCPS_4 Divider ratio 1:512

; WDTCPS = WDTCPS_5 Divider ratio 1:1024

; WDTCPS = WDTCPS_6 Divider ratio 1:2048

; WDTCPS = WDTCPS_7 Divider ratio 1:4096

; WDTCPS = WDTCPS_8 Divider ratio 1:8192

; WDTCPS = WDTCPS_9 Divider ratio 1:16384

; WDTCPS = WDTCPS_10 Divider ratio 1:32768

; WDTCPS = WDTCPS_11 Divider ratio 1:65536

; WDTCPS = WDTCPS_12 Divider ratio 1:131072

; WDTCPS = WDTCPS_13 Divider ratio 1:262144

; WDTCPS = WDTCPS_14 Divider ratio 1:524299

; WDTCPS = WDTCPS_15 Divider ratio 1:1048576

; WDTCPS = WDTCPS_16 Divider ratio 1:2097152

; WDTCPS = WDTCPS_17 Divider ratio 1:4194304

; WDTCPS = WDTCPS_18 Divider ratio 1:8388608

; WDTCPS = WDTCPS_19 Divider ratio 1:32

; WDTCPS = WDTCPS_20 Divider ratio 1:32

; WDTCPS = WDTCPS_21 Divider ratio 1:32

; WDTCPS = WDTCPS_22 Divider ratio 1:32

; WDTCPS = WDTCPS_23 Divider ratio 1:32

; WDTCPS = WDTCPS_24 Divider ratio 1:32

; WDTCPS = WDTCPS_25 Divider ratio 1:32

; WDTCPS = WDTCPS_26 Divider ratio 1:32

; WDTCPS = WDTCPS_27 Divider ratio 1:32

; WDTCPS = WDTCPS_28 Divider ratio 1:32

; WDTCPS = WDTCPS_29 Divider ratio 1:32

; WDTCPS = WDTCPS_30 Divider ratio 1:32

; WDTCPS = WDTCPS_31 Divider ratio 1:65536; software control of WDTPS

;

; WDT operating mode:

CONFIG WDTE = OFF ; WDT Disabled; SWDTEN is ignored

; WDTE = SWDTEN WDT enabled/disabled by SWDTEN bit

; WDTE = NSLEEP WDT enabled while sleep=0, suspended when sleep=1; SWDTEN ignored

; WDTE = ON WDT enabled regardless of sleep

;

; WDT Window Select bits:

; WDTCWS = WDTCWS_0 window delay = 87.5; no software control; keyed access required

; WDTCWS = WDTCWS_1 window delay = 75 percent of time; no software control; keyed access required

; WDTCWS = WDTCWS_2 window delay = 62.5 percent of time; no software control; keyed access required

; WDTCWS = WDTCWS_3 window delay = 50 percent of time; no software control; keyed access required

; WDTCWS = WDTCWS_4 window delay = 37.5 percent of time; no software control; keyed access required

; WDTCWS = WDTCWS_5 window delay = 25 percent of time; no software control; keyed access required

; WDTCWS = WDTCWS_6 window always open (100%); no software control; keyed access required

; WDTCWS = WDTCWS_7 window always open (100%); software control; keyed access not required

;

; WDT input clock selector:

; WDTCCS = LFINTOSC WDT reference clock is the 31.0 kHz LFINTOSC

; WDTCCS = MFINTOSC WDT reference clock is the 32kHz MFINTOSC output

; WDTCCS = SOSC WDT reference clock is SOSC

; WDTCCS = SC Software Control

;

; Boot Block Size selection bits:

; BBSIZE = BBSIZE_8192 Boot Block size is 8192 words

; BBSIZE = BBSIZE_4096 Boot Block size is 4096 words

; BBSIZE = BBSIZE_2048 Boot Block size is 2048 words

; BBSIZE = BBSIZE_1024 Boot Block size is 1024 words

; BBSIZE = BBSIZE_512 Boot Block size is 512 words

;

; Boot Block enable bit:

; BBEN = ON Boot block enabled

; BBEN = OFF Boot block disabled

;

; Storage Area Flash enable bit:

; SAFEN = ON SAF enabled

; SAFEN = OFF SAF disabled

;

; Application Block write protection bit:

; WRTAPP = ON Application Block write protected

; WRTAPP = OFF Application Block not write protected

;

; Configuration Register Write Protection bit:

; WRTB = ON Configuration registers (300000-30000Bh) write-protected

; WRTB = OFF Configuration registers (300000-30000Bh) not write-protected

;

; Boot Block Write Protection bit:

; WRTC = ON Boot Block (000000-0007FFh) write-protected

; WRTC = OFF Boot Block (000000-0007FFh) not write-protected

;

; Data EEPROM Write Protection bit:

; WRTD = ON Data EEPROM write-protected

; WRTD = OFF Data EEPROM not write-protected

;

; SAF Write protection bit:

; WRTSAF = ON SAF Write Protected

; WRTSAF = OFF SAF not Write Protected

;

; Low Voltage Programming Enable bit:

CONFIG LVP = OFF ; HV on MCLR/VPP must be used for programming

; LVP = ON Low voltage programming enabled. MCLR/VPP pin function is MCLR. MCLRE configuration bit is ignored

;

; PFM and Data EEPROM Code Protection bit:

; CP = ON PFM and Data EEPROM code protection enabled

; CP = OFF PFM and Data EEPROM code protection disabled

;-----------------------------------------------------------------------------------------------------------------

;-----------------------------------------------------------------------------------------------------------------

LIST P=PIC18F45K42 ; ISO 8859-2

#include p18f45k42.inc ;

CODE

global konfig ;

extern konfig_ ;

konfig:

;---------------------------------------------------------------------------------------------------------------

; ÓRAJRL BEÁLLÍTÁSA

; Belső nagyfrekvenviás (HFINOSC) oszcillátor beállítása

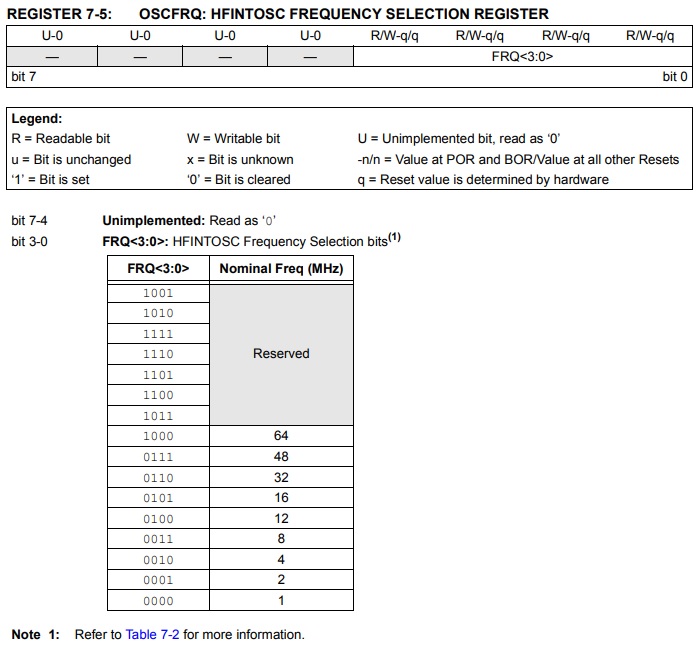

banksel OSCFRQ ; OSCFRQ<3:0>, OSCFRQ<7:4> nincs használva. Dok.:105 old.

movlw b'00000000' ; 1 MHz

; movlw b'00000001' ; 2 MHz

; movlw b'00000010' ; 4 MHz Ez az alapértelmezett ha nem állítjuk be

; movlw b'00000011' ; 8 MHz

; movlw b'00000100' ; 12 MHz

; movlw b'00000101' ; 16 MHz

; movlw b'00000110' ; 32 MHz

; movlw b'00000111' ; 48 MHz

; movlw b'00001000' ; 64 MHz

movwf OSCFRQ

;.......................................................................

; OSCCON1 beállítása:

; CPU órajel választás OSCCON1<6:4> (NOSC), osztás OSCCON1<3:0> (NDIV),

; nem használt OSCCON1<7> Dok.: 101-102. old,

;

; OSCCON1<6:4> NOSC<2:0>

; 010 - EXTOSC + 4x PLL ( Elsődleges külső oszcillátor 4xPLL-el)

; 100 - SOSC (Másodlagos oszcillátor /Timer1/)

; 101 - LFINTOSC (belső 31 KHz-es RC oszcillátor)

; 110 - HFINTOSC ( belső kalibrálható és választhaó frekvenciájú

; 1,2,4 8,12,16,32,48,64 MHz nagyfrekvenciájú oszcillátor

; 111 - EXTOSC ( Elsődleges külső oszcillátor vagy órajel 4XPLL nélkül )

; OSCCON1<3:0> NDIV<3:0> osztásarány (osztó)

; 0000 - 1

; 0001 - 2

; 0010 - 4

; 0011 - 8

; 0100 - 16

; 0101 - 32

; 0110 - 64

; 0111 - 128

; 1000 - 256

; 1001 - 512

banksel OSCCON1

movlw b'01100000' ;

movwf OSCCON1 ;

goto konfig_

;--------------------------------------------------------------------

; ide írjuk az egyéb konfigurációhoz a kódokat, pld TRISB megadása

END

Belső nagyfrekvenciás oszcillátor használata (HFINTOSC):

A program felső részébe a következőket konfigurációk lehetnek:

CONFIG FEXTOSC = OFF ; Külső oszcillator nincs engedelyezve (lehet, hogy ez csak az elsődleges oszcillátorra vonatkozik)

CONFIG RSTOSC = HFINTOSC_1MHZHFINTOSC ; with HFFRQ = 4 MHz and CDIV = 4:1 -

; RESET esetén: Magas frekvenciaju belso oszcillator ?????? kozepes frekvencias beallitassal

A OSCFRQ regiszter FRQ<3:0> bitekkel beállítható a HFINTOSC által kiadott ferkvencia lépéskben 1MHz-64MHz-ig.

A regiszter többi bitje nencs felhasználva. (Katalógus 107. old.)

OSCTUNE regiszter TUN<0:5> bitjeivel ezt az oszcillátort finomhangolhatjuk, ha fontos a nagyon pontos frekvencia. (Katalógus 108. old.) Tudtommal ez gyárilag be van finomhangolva, melynek az értékét programozás előtt érdemes kiolvasni és elmenteni. Persze ezt nem értem ha RAM területen van tárolva!

Az OSCEN regiszterrel egyenkét engedélyezhetők az oszcillátorok a 2-7. bitekkel. Így HFOEN = 1-el állításával kell engedélyezni a HFINTOSC oszcillátort. A többi oszcillátor is hasonlóan engedélyezhető. Részletek: Katalógus 108. old.

Az OSCCON2 regiszter COSC<2:0> bitjeinek beállításával kell megadni, hogy a CPU melyik órajel forrásból kapja meg az órajel, Esetünkben a SOSC<110>, amit az OSCCON2 regiszter <6:4> bitjei tárolnak majd. Katalógus 105. oldal. Táblázat: 103. old.

Az OSCCON2 regiszter CDIV<3:0> bitjeivel a Posz Mixer által leosztott ferkvenciák közül választható meg a CPU órajel. Itt OSCCON2 regiszter<3:0> bitjei tárolják az értéket. Katalógus 105. oldal. Táblázat: 103. old.

; External Oscillator Selection:

Kulso oszcillator vagy orajelvalasztas (Kat.: 66. old. Modulrajz: 93. old.)

; CONFIG FEXTOSC = LP ; LP (crystal oscillator) optimized for 32.768 kHz; PFM set to low power

; Alacsony frekvenciaju (32.768 kHz-re optimalizalt) kristaly oszcillator hasznalata

; CONFIG FEXTOSC = XT ; XT (crystal oscillator) above 100 kHz, below 8 MHz; PFM set to medium power

; Kozepes frekvenciaju (100kHz és 8 MHz kozott) kristaly oszcillator hasznalata

; CONFIG FEXTOSC = HS ; HS (crystal oscillator) above 8 MHz; PFM set to high power

; Magas frekvenciaju (8 MHz felett) kristaly oszcillator hasznalata

; CONFIG FEXTOSC = RESERVED ; Reserved (DO NOT USE) - Fenntartva (NE HASZNÁLD)

; CONFIG FEXTOSC = OFF ; Oscillator not enabled - Oszcillator nincs engedelyezve

; CONFIG FEXTOSC = ECL ; EC (external clock) below 100 kHz; PFM set to low power

; EC (external clock) vagyis kulso orajel 100 Khz alatt. Ilyenkor az egyik oszcillatollab felszabadul me celra.

; CONFIG FEXTOSC = ECM ; EC (external clock) for 500 kHz to 8 MHz; PFM set to medium power

; EC (external clock) vagyis kulso orajel 500 Khz es 8 MHz kozott. Ilyenkor az egyik oszcillatollab felszabadul me celra.

; CONFIG FEXTOSC = ECH ; EC (external clock) above 8 MHz; PFM set to high power

; EC (external clock) vagyis kulso orajel 8 Mhz felett. Ilyenkor az egyik oszcillatollab felszabadul me celra.

;

;

; Reset Oscillator Selection:

; Indulaskor mas orajelforras is lehet, amit itt lehet beallitani:

; CONFIG RSTOSC = HFINTOSC_64MHZHFINTOSC ; with HFFRQ = 64 MHz and CDIV = 1:1

; Magas frekvenciaju belso oszcillator magas ferkvencias beallitassal

; CONFIG RSTOSC = RESERVED_1 ; Reserved - Fenntartott. Ne haszmáljuk!

; CONFIG RSTOSC = EXTOSC_4PLL EXTOSC ; with 4x PLL, with EXTOSC operating per FEXTOSC bits

; CONFIG RSTOSC = RESERVED_2 ; Reserved - Fenntartott. Ne haszmáljuk!

; CONFIG RSTOSC = SOSC ; Secondary Oscillator - Masodlagos oszcillator (Timer0)

; CONFIG RSTOSC = LFINTOSC ; Low-Frequency Oscillator - Alacsony frekvenciaju belso oszcillator, ami 31 Khz-es belso oszcillator

; CONFIG RSTOSC = HFINTOSC_1MHZHFINTOSC ; with HFFRQ = 4 MHz and CDIV = 4:1 - Magas frekvenciaju belso oszcillator

; ?????? kozepes frekvencias beallitassal ;

; CONFIG RSTOSC = EXTOSC ; EXTOSC operating per FEXTOSC bits (device manufacturing default)

; Kulso oszcillatoros mukodes a fentebb beallitott FEXTOSC szerint. Nincs ketsebesseges indulas.

;Ez az alapertelmezett beallitas.

;

; Clock out Enable bit:

; CONFIG CLKOUTEN = ON ; CLKOUT function is enabled

; CONFIG CLKOUTEN = OFF ; CLKOUT function is disabled

;

; PRLOCKED One-Way Set Enable bit:

; CONFIG PR1WAY = OFF ; PRLOCK bit can be set and cleared repeatedly

; CONFIG PR1WAY = ON ; PRLOCK bit can be cleared and set only once

;

; Clock Switch Enable bit:

; CONFIG CSWEN = OFF ; The NOSC and NDIV bits cannot be changed by user software

; CONFIG CSWEN = ON ; Writing to NOSC and NDIV is allowed

;

; Fail-Safe Clock Monitor Enable bit:

; CPU orajelforras figyelesenek engedelyezese/tiltasa. Pld. ha a kulso oszcillator meghibasodik, azt tudja ezaltal erzekelni.

; Referenciaforrasnak az erzekelesre a 31 KHz-es TFINTOSC-ot hasznalja. Hiany eseten lehetoseg van beavatkozasra.

; CONFIG FCMEN = OFF ; Fail-Safe Clock Monitor disabled - Tiltja a CPU orajel figyelest

; CONFIG FCMEN = ON ; Fail-Safe Clock Monitor enabled - Engedelyezi a CPU orajel figyelest

; MCLR Enable bit: ???? at kell majd irni