- Címlap

- LED kijelzők meghajtása

- Permetező projekt

- PIC18FxxK42

- PIC18FxxK42 I2C regiszterei

- PIC18FxxK42 órajel beállítása

- Pic18FxxK42 regiszterei

- Láb hozzárendelés PIC18FxxK42

- Pic18 I2C programozás

- PIC18FxxK42 I2C kommunikáció

- EEPROM memória használata

- LIN UART-tal fordítás

- LM75A és PIC18F45K42 I2C1 program

- Objektumok

- Pic18FxxK42 konfigurálás

- SPI

- UART PIC18(L)F45K42

- Watchdog Timer

- PIC18F45K42 timer2,-4,-6

- I2C modul 1

- PIC18F45K22 I2C lépései

- PIC18F45K42 USART regiszterei és azok magyarázata II.

- PIC18F45K42 USART regiszterei

- PIC18F45K42 timer1,-3,-5

- UART PIC18F45K42

- PIC18 utasításkészlete

- USART mudullal aszinkron kapcsolat két mikrokontroller közt

- CAN kommunikáció

- DS3231SN RTC

- Dell T 5600

- E-paper

- EGYÉB jegyzet

- ESP 8266 WiFi modul

- ESP-07 ESP-12x

- ESP-12F WiFi modul

- ESP32

- ESP8266

- Egyéb (elektronika)

- Emeléskijelző projekt

- Giroszkóp

- HASZNOSAK

- Hasznos általános linkek

- Illesztő modulok

- Kapcsolások, megoldások

- Kiszajú műveleti erősítő

- Konfigurálás

- LIN kommunikáció UART-tal

- MPASM PIC18

- Nyomásmérés MS5803-05BA-val

- Nyomásmérő I2C

- Nyomásszenzor SPD8xx I2C

- Nyák, nyáktervezés

- Operációs rendszerek

- PIC 18 mikrokontrollerek

- PIC18(L)F47K40

- PIC18(L)F65K40

- PIC18F45(K)50

- PIC18F87k22(80 láb)

- PROGRAMOZÁS

- Programozás

- Python 3

- RAUCH 2057153

- RDS

- RTC TLC 5947-el

- Rádiókapcsolat két mikrokontroller között

- Számítógépes programok

- TCS34725 színérzékelő

- TLC 5947

- TTP223 kapacitív nyomógomb

- USB + USB AN1310-el

- Ulefone Power 2

- Vektoros megszakítások

- Vetőgép

- Webfejlesztés

- WiFi, Bluetooth modulok

- Pickit 3 programozó

- Pic-Ethernet-Pic

- LM75A

- PWM CCPx modullal

- PWM PWMx modullal

- NCO

- TCS 3200 RGB érzékelés

- Nyáktervezés

- Oktatás

- PIC 24 mikrokontrollerek

NCO

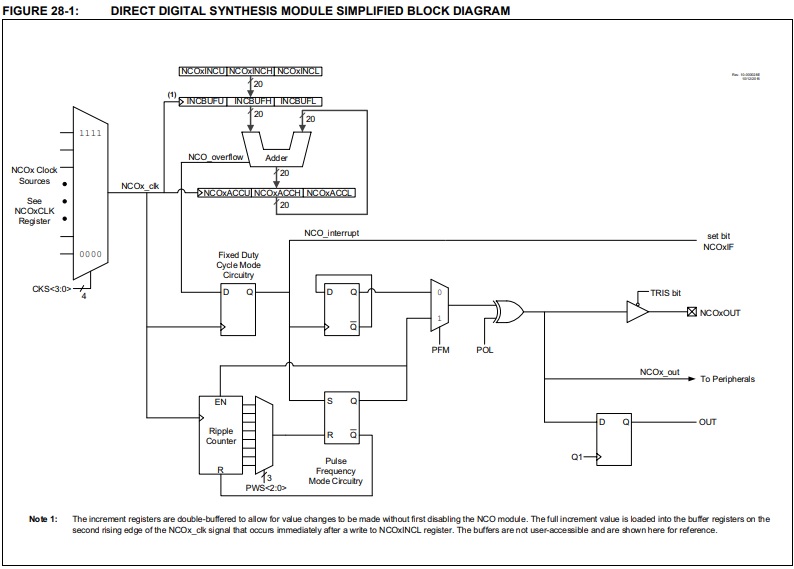

Számvezérelt oszcillátor modul

NUMERICALLY CONTROLLED OSCILLATOR (NCO) MODULE

NCO doksi (EN) : NCO doksi (PDF)

K:446. old

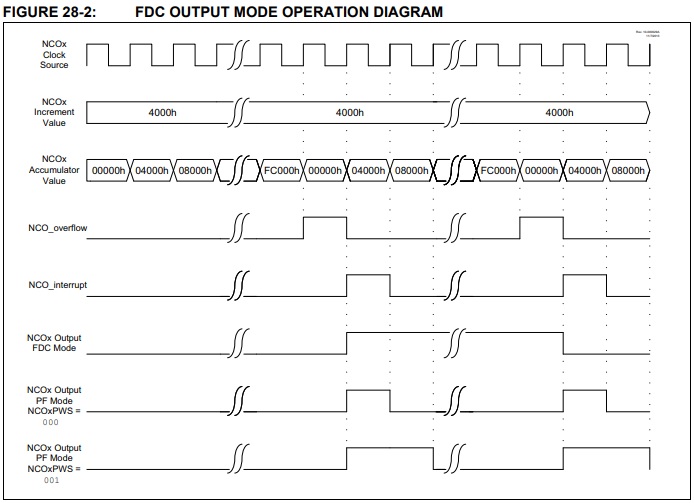

Működése:

- NCOxINCU-ba beírjuk a ferkvenciameghatározó értéket, majd NCOxINCH-ba és végül az NCOxINCL-be. Tehát itt adjuk meg, hogy mennyi legyen a kimeneten a frekvencia. A kimeneti frekvenciájára természetesen más értékek is hatással vannak, ezekről lentebb lehet olvasni. Ha a mudul nincs engedélyezve, akkor ez az adat a beírást követően átvándorol az INCBUFx regiszterekbe, ha engedélyezve van, akkor csak akkor, amikor a beírást követően a bemeneti órajel második felfutó éle történik.

- Az NCOxINCL regiszterbe történő írást követően az NCOx_clk jel második felfutó élekor azonnal átkerül az INCBUFx regiszterekbe az adat. Ez a kettős pufferezés teszi lehetővé, hogy az NCO modul működése közben is zökkenőmentesen tudjuk állítani ezt az értéket, vagyis a kimenet frekvenciájának értéket. Ha az NCO1 modul nincs engedélyezve, akkor ez az adatátvánsorlás azonnal bekövetkezik.

Az increment regiszterek dupla pufferrel vannak ellátva, hogy lehetővé tegyék az értékváltoztatásokat az NCO modul letiltása nélkül. A teljes inkrement érték az NCOx_clk jel második emelkedési élén lévő puffer regiszterbe kerül, amely az NCOxINCL regiszterbe történő írást követően azonnal megtörténik. A pufferek nem hozzáférhetőek a felhasználók számára, és itt hivatkozásként jelennek meg.

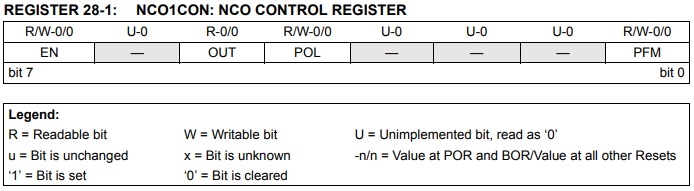

| 0. bit | PFM: NCO1 Pulse Frequency Mode bit A kimeneti impulzusok milyenségét beáálító bit

|

| 4. bit | POL: NCO1 Polarity A kimenet polaritását beállító bit

|

| 5. bit | OUT: NCO1 Output bit A kimenet ártékét felvevő (jelző) bit. Csak olvasható. |

| 7. bit | EN: NCO1 Enable bit NCO1 modult engedélyező (be/ki kapcsoló) bit

|

PÉLDAPROGRAM:

Főprogram:

LIST P=PIC18F45K42 ; ISO 8859-2

#include p18f45k42.inc ;

; Fosc = 8 MHz

adat: UDATA_ACS ; H'10' ; nincs kezdo memoriacim megadva az ACCESS ramban

W_TEMP RES 1 ; w register for context saving (ACCESS)

STATUS_TEMP RES 1 ; status used for context saving

BSR_TEMP RES 1 ; bank select used for ISR context saving

ORG 0X0000

nop

CODE

global konfig_

extern konfig

nop ;

goto start ;

;----------------------------------PIC18's--------------------------------------

; FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF

; NCO (számvezérelt oszcillátor) megvalósítása 500 KHz-es INTOSC órajellel

; hangfrekvenciás jelkeltés céljából. Alkalmazható például hangriasztásra.

start:

nop

foprogram:

goto konfig ;

nop

konfig_:

banksel NCO1ACCL

movlw b'0000' ;

movwf NCO1ACCU ;

movlw b'00000000' ;

movwf NCO1ACCH ;

movlw b'00000000' ;

movwf NCO1ACCL ;

banksel NCO1INCL ;

; 500KHz-es órajel frekvenciafelező üzemmódban k.b.:

movlw h'F' ; b'1100' ; NCO1INC=00-0Hz, 0001-0,4Hz, 010-0,5Hz, 011-1Hz

movwf NCO1INCU ; 100-1,5Hz, 1000-2,5Hz, 10000-4Hz, 100000-8Hz, 1000000-15Hz

; 10000000-30Hz, 01'00000000-61Hz, 10'0...0-122Hz,

movlw h'FF' ;b'00000000' ; 0100'0...0-245Hz, 01000'0-490Hz, 10000'0-977Hz,

movwf NCO1INCH ; 100000'0-1,96KHz, 1000000'0-3,91KHz, 10000000'0-7,82KHz,

; 01'0'0-15,6KHz, 010'0'0-31,3KHz, 0100'0'0-62,6KHz,

movlw h'FF' ;b'00000000' ; 1000'0'0-125,2KHz, 1000'0'00000001-125,3KHz,

movwf NCO1INCL ; 1100'0'0-187,9KHz, F'FF'FF-250,7KHz

goto $ ;

END

Konfiguráció:

LIST P=PIC18F45K42 ; ISO 8859-2

#include p18f45k42.inc ;

; External Oscillator Selection:

; FEXTOSC = LP LP (crystal oscillator) optimized for 32.768 kHz; PFM set to low power

; FEXTOSC = XT XT (crystal oscillator) above 100 kHz, below 8 MHz; PFM set to medium power

; FEXTOSC = HS HS (crystal oscillator) above 8 MHz; PFM set to high power

; FEXTOSC = RESERVED Reserved (DO NOT USE)

; CONFIG FEXTOSC = OFF ; Oscillator not enabled

; FEXTOSC = ECL EC (external clock) below 100 kHz; PFM set to low power

CONFIG FEXTOSC = ECM ; EC (external clock) for 500 kHz to 8 MHz; PFM set to medium power

; FEXTOSC = ECH EC (external clock) above 8 MHz; PFM set to high power

;

; Reset Oscillator Selection:

; RSTOSC = HFINTOSC_64MHZHFINTOSC with HFFRQ = 64 MHz and CDIV = 1:1

; RSTOSC = RESERVED_1 Reserved

; RSTOSC = EXTOSC_4PLL EXTOSC with 4x PLL, with EXTOSC operating per FEXTOSC bits

; RSTOSC = RESERVED_2 Reserved

; RSTOSC = SOSC Secondary Oscillator

; RSTOSC = LFINTOSC Low-Frequency Oscillator

; CONFIG RSTOSC = HFINTOSC_1MHZHFINTOSC ; with HFFRQ = 4 MHz and CDIV = 4:1

; RSTOSC = EXTOSC EXTOSC operating per FEXTOSC bits (device manufacturing default)

;

; Clock out Enable bit:

; CLKOUTEN = ON CLKOUT function is enabled

; CLKOUTEN = OFF CLKOUT function is disabled

;

; PRLOCKED One-Way Set Enable bit:

; PR1WAY = OFF PRLOCK bit can be set and cleared repeatedly

; CONFIG PR1WAY = ON ; PRLOCK bit can be cleared and set only once

;

; Clock Switch Enable bit:

; CSWEN = OFF The NOSC and NDIV bits cannot be changed by user software

; CSWEN = ON Writing to NOSC and NDIV is allowed

;

; Fail-Safe Clock Monitor Enable bit:

; FCMEN = OFF Fail-Safe Clock Monitor disabled

; FCMEN = ON Fail-Safe Clock Monitor enabled

;

; MCLR Enable bit:

; CONFIG MCLRE = INTMCLR ; If LVP = 0, MCLR pin function is port defined function; If LVP =1, RE3 pin fuction is MCLR

; MCLRE = EXTMCLR If LVP = 0, MCLR pin is MCLR; If LVP = 1, RE3 pin function is MCLR

;

; Power-up timer selection bits:

; PWRTS = PWRT_1 PWRT set at 1ms

; PWRTS = PWRT_16 PWRT set at 16ms

; PWRTS = PWRT_64 PWRT set at 64ms

; PWRTS = PWRT_OFF PWRT is disabled

;

; Multi-vector enable bit:

; CONFIG MVECEN = OFF ; Interrupt contoller does not use vector table to prioritze interrupts

; MVECEN = ON Multi-vector enabled, Vector table used for interrupts

;

; IVTLOCK bit One-way set enable bit:

; IVT1WAY = OFF IVTLOCK bit can be cleared and set repeatedly

; CONFIG IVT1WAY = ON ; IVTLOCK bit can be cleared and set only once

;

; Low Power BOR Enable bit:

; LPBOREN = ON ULPBOR enabled

CONFIG LPBOREN = OFF ; ULPBOR disabled

;

; Brown-out Reset Enable bits:

; BOREN = OFF Brown-out Reset disabled

; BOREN = ON Brown-out Reset enabled according to SBOREN

; BOREN = NOSLP Brown-out Reset enabled while running, disabled in Sleep; SBOREN is ignored

; BOREN = SBORDIS Brown-out Reset enabled , SBOREN bit is ignored

;

; Brown-out Reset Voltage Selection bits:

; BORV = VBOR_2P85 Brown-out Reset Voltage (VBOR) set to 2.8V

; BORV = VBOR_2P7 Brown-out Reset Voltage (VBOR) set to 2.7V

; BORV = VBOR_245 Brown-out Reset Voltage (VBOR) set to 2.45V

; BORV = VBOR_190 Brown-out Reset Voltage (VBOR) set to 1.90V

;

; ZCD Disable bit:

; ZCD = ON ZCD always enabled

; ZCD = OFF ZCD disabled. ZCD can be enabled by setting the ZCDSEN bit of ZCDCON

;

; PPSLOCK bit One-Way Set Enable bit:

CONFIG PPS1WAY = OFF ; PPSLOCK bit can be set and cleared repeatedly (subject to the unlock sequence)

; CONFIG PPS1WAY = ON ; PPSLOCK bit can be cleared and set only once; PPS registers remain locked after one clear/set cycle

;

; Stack Full/Underflow Reset Enable bit:

; STVREN = OFF Stack full/underflow will not cause Reset

CONFIG STVREN = ON ; Stack full/underflow will cause Reset

;

; Debugger Enable bit:

; DEBUG = ON Background debugger enabled

; DEBUG = OFF Background debugger disabled

;

; Extended Instruction Set Enable bit:

; XINST = ON Extended Instruction Set and Indexed Addressing Mode enabled

CONFIG XINST = OFF ; Extended Instruction Set and Indexed Addressing Mode disabled

;

; WDT Period selection bits:

; WDTCPS = WDTCPS_0 Divider ratio 1:32

; WDTCPS = WDTCPS_1 Divider ratio 1:64

; WDTCPS = WDTCPS_2 Divider ratio 1:128

; WDTCPS = WDTCPS_3 Divider ratio 1:256

; WDTCPS = WDTCPS_4 Divider ratio 1:512

; WDTCPS = WDTCPS_5 Divider ratio 1:1024

; WDTCPS = WDTCPS_6 Divider ratio 1:2048

; WDTCPS = WDTCPS_7 Divider ratio 1:4096

; WDTCPS = WDTCPS_8 Divider ratio 1:8192

; WDTCPS = WDTCPS_9 Divider ratio 1:16384

; WDTCPS = WDTCPS_10 Divider ratio 1:32768

; WDTCPS = WDTCPS_11 Divider ratio 1:65536

; WDTCPS = WDTCPS_12 Divider ratio 1:131072

; WDTCPS = WDTCPS_13 Divider ratio 1:262144

; WDTCPS = WDTCPS_14 Divider ratio 1:524299

; WDTCPS = WDTCPS_15 Divider ratio 1:1048576

; WDTCPS = WDTCPS_16 Divider ratio 1:2097152

; WDTCPS = WDTCPS_17 Divider ratio 1:4194304

; WDTCPS = WDTCPS_18 Divider ratio 1:8388608

; WDTCPS = WDTCPS_19 Divider ratio 1:32

; WDTCPS = WDTCPS_20 Divider ratio 1:32

; WDTCPS = WDTCPS_21 Divider ratio 1:32

; WDTCPS = WDTCPS_22 Divider ratio 1:32

; WDTCPS = WDTCPS_23 Divider ratio 1:32

; WDTCPS = WDTCPS_24 Divider ratio 1:32

; WDTCPS = WDTCPS_25 Divider ratio 1:32

; WDTCPS = WDTCPS_26 Divider ratio 1:32

; WDTCPS = WDTCPS_27 Divider ratio 1:32

; WDTCPS = WDTCPS_28 Divider ratio 1:32

; WDTCPS = WDTCPS_29 Divider ratio 1:32

; WDTCPS = WDTCPS_30 Divider ratio 1:32

; WDTCPS = WDTCPS_31 Divider ratio 1:65536; software control of WDTPS

;

; WDT operating mode:

CONFIG WDTE = OFF ; WDT Disabled; SWDTEN is ignored

; WDTE = SWDTEN WDT enabled/disabled by SWDTEN bit

; WDTE = NSLEEP WDT enabled while sleep=0, suspended when sleep=1; SWDTEN ignored

; WDTE = ON WDT enabled regardless of sleep

;

; WDT Window Select bits:

; WDTCWS = WDTCWS_0 window delay = 87.5; no software control; keyed access required

; WDTCWS = WDTCWS_1 window delay = 75 percent of time; no software control; keyed access required

; WDTCWS = WDTCWS_2 window delay = 62.5 percent of time; no software control; keyed access required

; WDTCWS = WDTCWS_3 window delay = 50 percent of time; no software control; keyed access required

; WDTCWS = WDTCWS_4 window delay = 37.5 percent of time; no software control; keyed access required

; WDTCWS = WDTCWS_5 window delay = 25 percent of time; no software control; keyed access required

; WDTCWS = WDTCWS_6 window always open (100%); no software control; keyed access required

; WDTCWS = WDTCWS_7 window always open (100%); software control; keyed access not required

;

; WDT input clock selector:

; WDTCCS = LFINTOSC WDT reference clock is the 31.0 kHz LFINTOSC

; WDTCCS = MFINTOSC WDT reference clock is the 32kHz MFINTOSC output

; WDTCCS = SOSC WDT reference clock is SOSC

; WDTCCS = SC Software Control

;

; Boot Block Size selection bits:

; BBSIZE = BBSIZE_8192 Boot Block size is 8192 words

; BBSIZE = BBSIZE_4096 Boot Block size is 4096 words

; BBSIZE = BBSIZE_2048 Boot Block size is 2048 words

; BBSIZE = BBSIZE_1024 Boot Block size is 1024 words

; BBSIZE = BBSIZE_512 Boot Block size is 512 words

;

; Boot Block enable bit:

; BBEN = ON Boot block enabled

; BBEN = OFF Boot block disabled

;

; Storage Area Flash enable bit:

; SAFEN = ON SAF enabled

; SAFEN = OFF SAF disabled

;

; Application Block write protection bit:

; WRTAPP = ON Application Block write protected

; WRTAPP = OFF Application Block not write protected

;

; Configuration Register Write Protection bit:

; WRTB = ON Configuration registers (300000-30000Bh) write-protected

; WRTB = OFF Configuration registers (300000-30000Bh) not write-protected

;

; Boot Block Write Protection bit:

; WRTC = ON Boot Block (000000-0007FFh) write-protected

; WRTC = OFF Boot Block (000000-0007FFh) not write-protected

;

; Data EEPROM Write Protection bit:

; WRTD = ON Data EEPROM write-protected

; WRTD = OFF Data EEPROM not write-protected

;

; SAF Write protection bit:

; WRTSAF = ON SAF Write Protected

; WRTSAF = OFF SAF not Write Protected

;

; Low Voltage Programming Enable bit:

CONFIG LVP = OFF ; HV on MCLR/VPP must be used for programming

; LVP = ON Low voltage programming enabled. MCLR/VPP pin function is MCLR. MCLRE configuration bit is ignored

;

; PFM and Data EEPROM Code Protection bit:

; CP = ON PFM and Data EEPROM code protection enabled

; CP = OFF PFM and Data EEPROM code protection disabled

;---Konfigurálás---------------------------------------------

CODE ;

extern konfig_

global konfig

konfig:

;---NCO------- K:446. old-------------------------------------

; Kimenetre a Pic18F45K42-nél az A vagy D port használható fel ( RD1-20.láb )

; Az RD1-20. lábat digitalissnak konfiguraljuk

banksel ANSELD ;

bcf ANSELD,ANSELD1 ; 20.lab { Katalógus 6, 11.old. es 264. oldal

;.........PWMx (NCO jelek) hozzarendelése a 20-as IC lábhoz.........

; Letiltjuk globalisan a megszakitasokat

banksel INTCON0

bcf INTCON0,GIE ; letiltjuk globálisan a megszakításokat

; PPS UNLOCK szekvencia

banksel PPSLOCK ;

movlw 0x55 ;

movwf PPSLOCK ;

movlw 0xAA ;

movwf PPSLOCK ;

; bcf PPSLOCK,PPSLOCKED ;

bcf PPSLOCK,0 ;

; Engedélyezzuk globalisan a megszakitasokat

banksel INTCON0

bsf INTCON0,GIE ; engedélyezzük globálisan a megszakításokat

; 20.láb = RD1 láb NCO modul kimenet

movlw b'100110' ; RD1 láb NCO modul kimenetéhez rendelése

banksel RD1PPS ;

movwf RD1PPS ; Kat.: 279. old

; Letiltjuk globálisan a megszakításokat

banksel INTCON0

bcf INTCON0,GIE ; letiltjuk globálisan a megszakításokat

; PPS LOCK szekvencia

banksel PPSLOCK ;

movlw 0x55 ;

movwf PPSLOCK ;

movlw 0xAA ;

movwf PPSLOCK ;

; bsf PPSLOCK,PPSLOCKED ;

bsf PPSLOCK,0 ;

; Engedélyezzuk globálisan a megszakításokat

banksel INTCON0

bsf INTCON0,GIE ; engedélyezzuk globálisan a megszakításokat

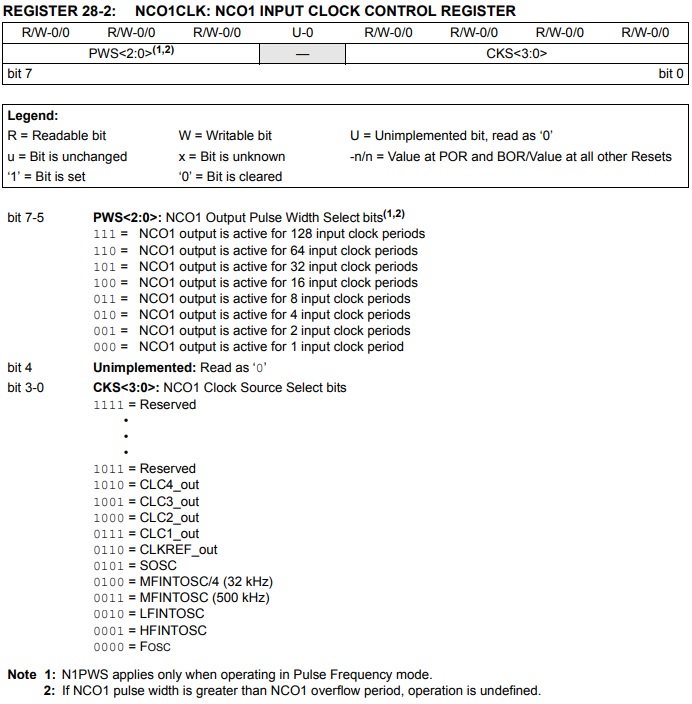

; NCO1CLK<3:0> (CKS<3:0>)

; NCO1 órajel forrást beállító bitek

; 1111 = Reserved

; ?

; 1011 = Reserved

; 1010 = CLC4_out

; 1001 = CLC3_out

; 1000 = CLC2_out

; 0111 = CLC1_out

; 0110 = CLKREF_out

; 0101 = SOSC

; 0100 = MFINTOSC/4 (32 kHz)

; 0011 = MFINTOSC (500 kHz)

; 0010 = LFINTOSC

; 0001 = HFINTOSC

; 0000 = FOSC

; NCO1CLK<4> nem használt

; NCO1CLK<7:5> (PWS<2:0>)

; NCO1 Output Pulse Width Select bits

; 111 = NCO1 output is active for 128 input clock periods

; 110 = NCO1 output is active for 64 input clock periods

; 101 = NCO1 output is active for 32 input clock periods

; 100 = NCO1 output is active for 16 input clock periods

; 011 = NCO1 output is active for 8 input clock periods

; 010 = NCO1 output is active for 4 input clock periods

; 001 = NCO1 output is active for 2 input clock periods

; 000 = NCO1 output is active for 1 input clock period

movlw b'00000011' ; 500 KHz INTOSC használata

banksel NCO1CLK ; 16 periódus

movwf NCO1CLK

; NCO1CON<7:0> beállítása

; <7> - EN:

; 1 = NCO1 module is enabled

; 0 = NCO1 module is disabled

; <6> - nem használt

; <5> - OUT:

; NCO1 Output bit

; Displays the current output value of the NCO1 module.

; <4> - POL:

; NCO1 Polarity

; 1 = NCO1 output signal is inverted

; 0 = NCO1 output signal is not inverted

; <3:1> Unimplemented

; <0> - PFM:

; NCO1 Pulse Frequency Mode bit

; 1 = NCO1 operates in Pulse Frequency mode

; 0 = NCO1operates in Fixed Duty Cycle mode, divide by 2

movlw b'10000000' ;

banksel NCO1CON ;

movwf NCO1CON ;

banksel TRISD

bcf TRISD,1

goto konfig_

END