- Címlap

- LED kijelzők meghajtása

- Permetező projekt

- PIC18FxxK42

- PIC18FxxK42 I2C regiszterei

- PIC18FxxK42 órajel beállítása

- Pic18FxxK42 regiszterei

- Láb hozzárendelés PIC18FxxK42

- Pic18 I2C programozás

- PIC18FxxK42 I2C kommunikáció

- EEPROM memória használata

- LIN UART-tal fordítás

- LM75A és PIC18F45K42 I2C1 program

- Objektumok

- Pic18FxxK42 konfigurálás

- SPI

- UART PIC18(L)F45K42

- Watchdog Timer

- PIC18F45K42 timer2,-4,-6

- I2C modul 1

- PIC18F45K22 I2C lépései

- PIC18F45K42 USART regiszterei és azok magyarázata II.

- PIC18F45K42 USART regiszterei

- PIC18F45K42 timer1,-3,-5

- UART PIC18F45K42

- PIC18 utasításkészlete

- USART mudullal aszinkron kapcsolat két mikrokontroller közt

- CAN kommunikáció

- DS3231SN RTC

- Dell T 5600

- E-paper

- EGYÉB jegyzet

- ESP 8266 WiFi modul

- ESP-07 ESP-12x

- ESP-12F WiFi modul

- ESP32

- ESP8266

- Egyéb (elektronika)

- Emeléskijelző projekt

- Giroszkóp

- HASZNOSAK

- Hasznos általános linkek

- Illesztő modulok

- Kapcsolások, megoldások

- Kiszajú műveleti erősítő

- Konfigurálás

- LIN kommunikáció UART-tal

- MPASM PIC18

- Nyomásmérés MS5803-05BA-val

- Nyomásmérő I2C

- Nyomásszenzor SPD8xx I2C

- Nyák, nyáktervezés

- Operációs rendszerek

- PIC 18 mikrokontrollerek

- PIC18(L)F47K40

- PIC18(L)F65K40

- PIC18F45(K)50

- PIC18F87k22(80 láb)

- PROGRAMOZÁS

- Programozás

- Python 3

- RAUCH 2057153

- RDS

- RTC TLC 5947-el

- Rádiókapcsolat két mikrokontroller között

- Számítógépes programok

- TCS34725 színérzékelő

- TLC 5947

- TTP223 kapacitív nyomógomb

- USB + USB AN1310-el

- Ulefone Power 2

- Vektoros megszakítások

- Vetőgép

- Webfejlesztés

- WiFi, Bluetooth modulok

- Pickit 3 programozó

- Pic-Ethernet-Pic

- LM75A

- PWM CCPx modullal

- PWM PWMx modullal

- NCO

- TCS 3200 RGB érzékelés

- Nyáktervezés

- Oktatás

- PIC 24 mikrokontrollerek

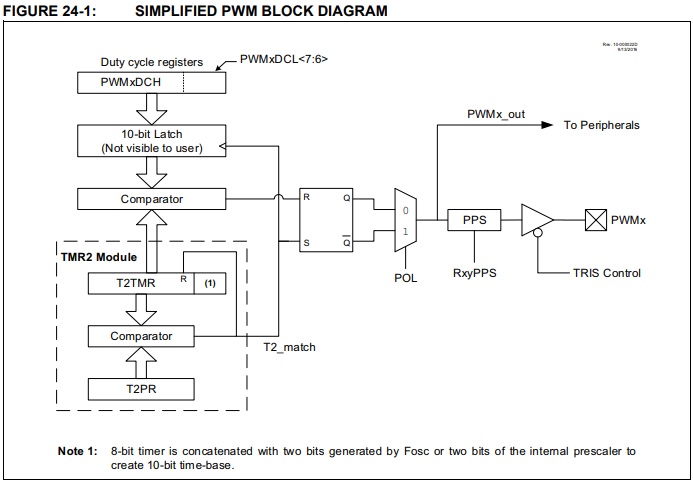

PWM PWMx modullal

PWM szabályozás PWMx modullal Pic18F45K42 mikrokontroller esetében

Példaprogram CCP1 modullal:

Pőprogram:

LIST P=PIC18F45K42 ; ISO 8859-2

#include p18f45k42.inc ;

; Fosc = 8 MHz

adat: UDATA_ACS ; H'10' ; nincs kezdo memoriacim megadva az ACCESS ramban

W_TEMP RES 1 ; w register for context saving (ACCESS)

STATUS_TEMP RES 1 ; status used for context saving

BSR_TEMP RES 1 ; bank select used for ISR context saving

ORG 0X0000

nop

CODE

global konfig_

extern konfig

nop ;

goto start ;

;----------------------------------PIC18's--------------------------------------

; FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF

; PWM kat:317-337. old. (Timer2) és 343-351 . old (CCPx).

start:

nop

foprogram:

goto konfig ;

nop

konfig_:

; Körülbelül 50%-os kitültéssel 30 Hz PWM jel

movlw b'0' ;

banksel PWM5DCL ; A 7:6 bit képezi a 10 bit 1:0 bitjét, a többi hatástalan

movwf PWM5DCL ;

movlw b'10000000' ; A 7:0 bit képezi a 10 bit 9:2 bitjét

movwf PWM5DCH ;

; Körülbelül nagy%-os kitültéssel 30 Hz PWM jel

movlw b'0' ;

banksel PWM6DCL

movwf PWM6DCL ;

movlw b'11000000' ; A 2 lacsony helyiértékű bit számít FMT = 0 esetén

movwf PWM6DCH ;

; Körülbelül kicsi%-os kitültéssel 30 Hz PWM jel

movlw b'0' ;

banksel PWM7DCL

movwf PWM7DCL ;

movlw b'01000000' ; A 2 lacsony helyiértékű bit számít FMT = 0 esetén

movwf PWM7DCH ;

; Körülbelül 50%-os kitültéssel 30 Hz PWM jel

movlw b'0' ;

banksel PWM8DCL

movwf PWM8DCL ;

movlw b'10000000' ; A 2 lacsony helyiértékű bit számít FMT = 0 esetén

movwf PWM8DCH ;

goto $ ;

END

Konfigurációs utasítások:

LIST P=PIC18F45K42 ; ISO 8859-2

#include p18f45k42.inc ;

; External Oscillator Selection:

; FEXTOSC = LP LP (crystal oscillator) optimized for 32.768 kHz; PFM set to low power

; FEXTOSC = XT XT (crystal oscillator) above 100 kHz, below 8 MHz; PFM set to medium power

; FEXTOSC = HS HS (crystal oscillator) above 8 MHz; PFM set to high power

; FEXTOSC = RESERVED Reserved (DO NOT USE)

; CONFIG FEXTOSC = OFF ; Oscillator not enabled

; FEXTOSC = ECL EC (external clock) below 100 kHz; PFM set to low power

CONFIG FEXTOSC = ECM ; EC (external clock) for 500 kHz to 8 MHz; PFM set to medium power

; FEXTOSC = ECH EC (external clock) above 8 MHz; PFM set to high power

;

; Reset Oscillator Selection:

; RSTOSC = HFINTOSC_64MHZHFINTOSC with HFFRQ = 64 MHz and CDIV = 1:1

; RSTOSC = RESERVED_1 Reserved

; RSTOSC = EXTOSC_4PLL EXTOSC with 4x PLL, with EXTOSC operating per FEXTOSC bits

; RSTOSC = RESERVED_2 Reserved

; RSTOSC = SOSC Secondary Oscillator

; RSTOSC = LFINTOSC Low-Frequency Oscillator

; CONFIG RSTOSC = HFINTOSC_1MHZHFINTOSC ; with HFFRQ = 4 MHz and CDIV = 4:1

; RSTOSC = EXTOSC EXTOSC operating per FEXTOSC bits (device manufacturing default)

;

; Clock out Enable bit:

; CLKOUTEN = ON CLKOUT function is enabled

; CLKOUTEN = OFF CLKOUT function is disabled

;

; PRLOCKED One-Way Set Enable bit:

; PR1WAY = OFF PRLOCK bit can be set and cleared repeatedly

; CONFIG PR1WAY = ON ; PRLOCK bit can be cleared and set only once

;

; Clock Switch Enable bit:

; CSWEN = OFF The NOSC and NDIV bits cannot be changed by user software

; CSWEN = ON Writing to NOSC and NDIV is allowed

;

; Fail-Safe Clock Monitor Enable bit:

; FCMEN = OFF Fail-Safe Clock Monitor disabled

; FCMEN = ON Fail-Safe Clock Monitor enabled

;

; MCLR Enable bit:

; CONFIG MCLRE = INTMCLR ; If LVP = 0, MCLR pin function is port defined function; If LVP =1, RE3 pin fuction is MCLR

; MCLRE = EXTMCLR If LVP = 0, MCLR pin is MCLR; If LVP = 1, RE3 pin function is MCLR

;

; Power-up timer selection bits:

; PWRTS = PWRT_1 PWRT set at 1ms

; PWRTS = PWRT_16 PWRT set at 16ms

; PWRTS = PWRT_64 PWRT set at 64ms

; PWRTS = PWRT_OFF PWRT is disabled

;

; Multi-vector enable bit:

; CONFIG MVECEN = OFF ; Interrupt contoller does not use vector table to prioritze interrupts

; MVECEN = ON Multi-vector enabled, Vector table used for interrupts

;

; IVTLOCK bit One-way set enable bit:

; IVT1WAY = OFF IVTLOCK bit can be cleared and set repeatedly

; CONFIG IVT1WAY = ON ; IVTLOCK bit can be cleared and set only once

;

; Low Power BOR Enable bit:

; LPBOREN = ON ULPBOR enabled

CONFIG LPBOREN = OFF ; ULPBOR disabled

;

; Brown-out Reset Enable bits:

; BOREN = OFF Brown-out Reset disabled

; BOREN = ON Brown-out Reset enabled according to SBOREN

; BOREN = NOSLP Brown-out Reset enabled while running, disabled in Sleep; SBOREN is ignored

; BOREN = SBORDIS Brown-out Reset enabled , SBOREN bit is ignored

;

; Brown-out Reset Voltage Selection bits:

; BORV = VBOR_2P85 Brown-out Reset Voltage (VBOR) set to 2.8V

; BORV = VBOR_2P7 Brown-out Reset Voltage (VBOR) set to 2.7V

; BORV = VBOR_245 Brown-out Reset Voltage (VBOR) set to 2.45V

; BORV = VBOR_190 Brown-out Reset Voltage (VBOR) set to 1.90V

;

; ZCD Disable bit:

; ZCD = ON ZCD always enabled

; ZCD = OFF ZCD disabled. ZCD can be enabled by setting the ZCDSEN bit of ZCDCON

;

; PPSLOCK bit One-Way Set Enable bit:

CONFIG PPS1WAY = OFF ; PPSLOCK bit can be set and cleared repeatedly (subject to the unlock sequence)

; CONFIG PPS1WAY = ON ; PPSLOCK bit can be cleared and set only once; PPS registers remain locked after one clear/set cycle

;

; Stack Full/Underflow Reset Enable bit:

; STVREN = OFF Stack full/underflow will not cause Reset

CONFIG STVREN = ON ; Stack full/underflow will cause Reset

;

; Debugger Enable bit:

; DEBUG = ON Background debugger enabled

; DEBUG = OFF Background debugger disabled

;

; Extended Instruction Set Enable bit:

; XINST = ON Extended Instruction Set and Indexed Addressing Mode enabled

CONFIG XINST = OFF ; Extended Instruction Set and Indexed Addressing Mode disabled

;

; WDT Period selection bits:

; WDTCPS = WDTCPS_0 Divider ratio 1:32

; WDTCPS = WDTCPS_1 Divider ratio 1:64

; WDTCPS = WDTCPS_2 Divider ratio 1:128

; WDTCPS = WDTCPS_3 Divider ratio 1:256

; WDTCPS = WDTCPS_4 Divider ratio 1:512

; WDTCPS = WDTCPS_5 Divider ratio 1:1024

; WDTCPS = WDTCPS_6 Divider ratio 1:2048

; WDTCPS = WDTCPS_7 Divider ratio 1:4096

; WDTCPS = WDTCPS_8 Divider ratio 1:8192

; WDTCPS = WDTCPS_9 Divider ratio 1:16384

; WDTCPS = WDTCPS_10 Divider ratio 1:32768

; WDTCPS = WDTCPS_11 Divider ratio 1:65536

; WDTCPS = WDTCPS_12 Divider ratio 1:131072

; WDTCPS = WDTCPS_13 Divider ratio 1:262144

; WDTCPS = WDTCPS_14 Divider ratio 1:524299

; WDTCPS = WDTCPS_15 Divider ratio 1:1048576

; WDTCPS = WDTCPS_16 Divider ratio 1:2097152

; WDTCPS = WDTCPS_17 Divider ratio 1:4194304

; WDTCPS = WDTCPS_18 Divider ratio 1:8388608

; WDTCPS = WDTCPS_19 Divider ratio 1:32

; WDTCPS = WDTCPS_20 Divider ratio 1:32

; WDTCPS = WDTCPS_21 Divider ratio 1:32

; WDTCPS = WDTCPS_22 Divider ratio 1:32

; WDTCPS = WDTCPS_23 Divider ratio 1:32

; WDTCPS = WDTCPS_24 Divider ratio 1:32

; WDTCPS = WDTCPS_25 Divider ratio 1:32

; WDTCPS = WDTCPS_26 Divider ratio 1:32

; WDTCPS = WDTCPS_27 Divider ratio 1:32

; WDTCPS = WDTCPS_28 Divider ratio 1:32

; WDTCPS = WDTCPS_29 Divider ratio 1:32

; WDTCPS = WDTCPS_30 Divider ratio 1:32

; WDTCPS = WDTCPS_31 Divider ratio 1:65536; software control of WDTPS

;

; WDT operating mode:

CONFIG WDTE = OFF ; WDT Disabled; SWDTEN is ignored

; WDTE = SWDTEN WDT enabled/disabled by SWDTEN bit

; WDTE = NSLEEP WDT enabled while sleep=0, suspended when sleep=1; SWDTEN ignored

; WDTE = ON WDT enabled regardless of sleep

;

; WDT Window Select bits:

; WDTCWS = WDTCWS_0 window delay = 87.5; no software control; keyed access required

; WDTCWS = WDTCWS_1 window delay = 75 percent of time; no software control; keyed access required

; WDTCWS = WDTCWS_2 window delay = 62.5 percent of time; no software control; keyed access required

; WDTCWS = WDTCWS_3 window delay = 50 percent of time; no software control; keyed access required

; WDTCWS = WDTCWS_4 window delay = 37.5 percent of time; no software control; keyed access required

; WDTCWS = WDTCWS_5 window delay = 25 percent of time; no software control; keyed access required

; WDTCWS = WDTCWS_6 window always open (100%); no software control; keyed access required

; WDTCWS = WDTCWS_7 window always open (100%); software control; keyed access not required

;

; WDT input clock selector:

; WDTCCS = LFINTOSC WDT reference clock is the 31.0 kHz LFINTOSC

; WDTCCS = MFINTOSC WDT reference clock is the 32kHz MFINTOSC output

; WDTCCS = SOSC WDT reference clock is SOSC

; WDTCCS = SC Software Control

;

; Boot Block Size selection bits:

; BBSIZE = BBSIZE_8192 Boot Block size is 8192 words

; BBSIZE = BBSIZE_4096 Boot Block size is 4096 words

; BBSIZE = BBSIZE_2048 Boot Block size is 2048 words

; BBSIZE = BBSIZE_1024 Boot Block size is 1024 words

; BBSIZE = BBSIZE_512 Boot Block size is 512 words

;

; Boot Block enable bit:

; BBEN = ON Boot block enabled

; BBEN = OFF Boot block disabled

;

; Storage Area Flash enable bit:

; SAFEN = ON SAF enabled

; SAFEN = OFF SAF disabled

;

; Application Block write protection bit:

; WRTAPP = ON Application Block write protected

; WRTAPP = OFF Application Block not write protected

;

; Configuration Register Write Protection bit:

; WRTB = ON Configuration registers (300000-30000Bh) write-protected

; WRTB = OFF Configuration registers (300000-30000Bh) not write-protected

;

; Boot Block Write Protection bit:

; WRTC = ON Boot Block (000000-0007FFh) write-protected

; WRTC = OFF Boot Block (000000-0007FFh) not write-protected

;

; Data EEPROM Write Protection bit:

; WRTD = ON Data EEPROM write-protected

; WRTD = OFF Data EEPROM not write-protected

;

; SAF Write protection bit:

; WRTSAF = ON SAF Write Protected

; WRTSAF = OFF SAF not Write Protected

;

; Low Voltage Programming Enable bit:

CONFIG LVP = OFF ; HV on MCLR/VPP must be used for programming

; LVP = ON Low voltage programming enabled. MCLR/VPP pin function is MCLR. MCLRE configuration bit is ignored

;

; PFM and Data EEPROM Code Protection bit:

; CP = ON PFM and Data EEPROM code protection enabled

; CP = OFF PFM and Data EEPROM code protection disabled

;---Konfigurálás---------------------------------------------

CODE ;

extern konfig_

global konfig

konfig:

;---PWMx_PWMx-------- K:352. old-------------------------------------

; A labalat ( RA0-2, RA1-3, RA2-4, RA3-5.lab) digitalissnak konfiguraljuk

banksel ANSELA ;

bcf ANSELA,ANSELA0 ; 2.lab { Katalógus 6, 11.old. es 264. oldal } HIBA

bcf ANSELA,ANSELA1 ; 3.lab { Katalógus 6, 11.old. es 264. oldal }

bcf ANSELA,ANSELA2 ; 4.lab { Katalógus 6, 11.old. es 264. oldal }

bcf ANSELA,ANSELA3 ; 5.lab { Katalógus 6, 11.old. es 264. oldal }

;.........PWMx (PWM jelek) hozzarendelése a 2, 3, 4, 5-ös IC lábhoz.........

; Letiltjuk globalisan a megszakitasokat

banksel INTCON0

bcf INTCON0,GIE ; letiltjuk globálisan a megszakításokat

; PPS UNLOCK szekvencia

banksel PPSLOCK ;

movlw 0x55 ;

movwf PPSLOCK ;

movlw 0xAA ;

movwf PPSLOCK ;

; bcf PPSLOCK,PPSLOCKED ;

bcf PPSLOCK,0 ;

; Engedélyezzuk globalisan a megszakitasokat

banksel INTCON0

bsf INTCON0,GIE ; engedélyezzük globálisan a megszakításokat

; 2.láb = RA0 láb PWM1 modul -> PWM5 jel

movlw b'001101' ; CCP1 kimenet (PWM1 jel) lábhoz rendelése

banksel RA0PPS ;

movwf RA0PPS ; Kat.: 280. old

; 3.láb = RA1 láb PWM2 modul -> PWM6 jel

movlw b'001110' ; CCP2 kimenet (PWM2 jel) lábhoz rendelése

; banksel RA1PPS ;

movwf RA1PPS ; Kat.: 280. old

; 4.láb = RA2 láb PWM3 modul -> PWM7 jel

movlw b'001111' ; CCP3 kimenet (PWM3 jel) lábhoz rendelése

; banksel RA2PPS ;

movwf RA2PPS ; Kat.: 280. old

; 5.láb = RA3 láb PWM4 modul -> PWM8 jel

movlw b'010000' ; CCP4 kimenet (PWM4 jel) lábhoz rendelése

; banksel RA3PPS ;

movwf RA3PPS ; Kat.: 280. old

; Letiltjuk globálisan a megszakításokat

banksel INTCON0

bcf INTCON0,GIE ; letiltjuk globálisan a megszakításokat

; PPS LOCK szekvencia

banksel PPSLOCK ;

movlw 0x55 ;

movwf PPSLOCK ;

movlw 0xAA ;

movwf PPSLOCK ;

; bsf PPSLOCK,PPSLOCKED ;

bsf PPSLOCK,0 ;

; Engedélyezzuk globálisan a megszakításokat

banksel INTCON0

bsf INTCON0,GIE ; engedélyezzuk globálisan a megszakításokat

; .............................................................

; CCPTMRS1<7:6> (T8TSEL<1:0>) PWM8 Timer választás

; 11 = PWM1 modul (PWM8 jel) hozzárendelése Timer6-hoz

; 10 = PWM1 modul (PWM8 jel)hozzárendelése Timer4-hez

; 01 = PWM1 modul (PWM8 jel)hozzárendelése Timer2-höz

; 00 = Reserved

; CCPTMRS1<5:4> (T7TSEL<1:0>) PWM7 Timer választás

; 11 = PWM2 modul (PWM7 jel)hozzárendelése Timer6-hoz

; 10 = PWM2 modul (PWM7 jel)hozzárendelése Timer4-hez

; 01 = PWM2 modul (PWM7 jel)hozzárendelése Timer2-höz

; 00 = Reserved

; CCPTMRS1<3:2> (T6TSEL<1:0>) PWM6 Timer választás

; 11 = PWM3 modul (PWM6 jel)hozzárendelése Timer6-hoz

; 10 = PWM3 modul (PWM6 jel)hozzárendelése Timer4-hez

; 01 = PWM3 modul (PWM6 jel)hozzárendelése Timer2-höz

; 00 = Reserved

; CCPTMRS1<1:0> (T5TSEL<1:0>) PWM5 Timer választás

; 11 = PWM4 modul (PWM5 jel)hozzárendelése Timer6-hoz

; 10 = PWM4 modul (PWM5 jel)hozzárendelése Timer4-hez

; 01 = PWM4 modul (PWM5 jel)hozzárendelése Timer2-höz

; 00 = Reserved

movlw b'11100101' ; { PWM1 és PWM2 modul (PWM5 és PWM6 jel)<-> Timer2

banksel CCPTMRS1 ; PWM3 modul (PWM7 jel) <-> Timer4

movwf CCPTMRS1 ; PWM4 modul (PWM8 jel) <-> Timer6 }

;.........................................

; Óral forrás választási lehetőségek:

; movlw b'0000' ; T2INPPS-el beállított lábról kapja az órajelet

; movlw b'0001' ; Fosc/4 (CPU órajel/4, vagyis műveletvégzési frekvencia)

; movlw b'0010' ; Fosc (CPU órajel) legyen a TIMER2 órajele

; movlw b'0011' ; HFINTOSC-ról (OSCFRQ<3:0>-val beállított) kapja az órajelet

; movlw b'0100' ; LFINTOSC-ról (alacsony frekvenviájó belső oszcillátor)

; movlw b'0101' ; MFINTOSC (500 KHz)-ról kapja az órajelet

; movlw b'0110' ; MFINTOSC (32 KHz)-ről kapja az órajelet

; movlw b'0111' ; SOSC (másodlagos /külső/ oszcillátor)

; movlw b'1000' ; CLKREF_OUT-ról kapja az órajelet

; movlw b'1001' ; NCO1OUT

; movlw b'1010' ; ZCD_OUT

; movlw b'1011' ; CLC1_out

; movlw b'1100' ; CLC2_out

; movlw b'1101' ; CLC3_out

; movlw b'1110' ; CLC4_out

movlw b'0001' ; Fosc/4 (CPU órajel/4, vagyis műveletvégzési frekvencia)

banksel T2CLK ;

movwf T2CLK ; A TMR2 órajel forrásának megadása

movlw b'0010' ; Fosc (CPU órajele)

banksel T4CLK ;

movwf T4CLK ; A TMR4 órajel forrásának megadása

movlw b'0101' ; MFINTOSC (500 KHz)-ról kapja az órajelet

banksel T6CLK ;

movwf T6CLK ; A TMR6 órajel forrásának megadása

; TMR2 modul beállítása

; TxCON<6:4> (CKPS<2:0>) előosztó (Megj.: utóoasztó nincs befolyással)

; 111 = 1:128 Prescaler

; 110 = 1:64 Prescaler

; 101 = 1:32 Prescaler

; 100 = 1:16 Prescaler

; 011 = 1:8 Prescaler

; 010 = 1:4 Prescaler

; 001 = 1:2 Prescaler

; 000 = 1:1 Prescaler

; ..TMR2..............

movlw b'01110000' ; <3:0>=utóosztó, <6:4>=előosztó, <7>=1 start, 0 stop

banksel T2CON ; előosztást 1:128-ra állítom (111) értékkel

movwf T2CON ; Megj.: Az utóosztó nincs hatássat a PWM működésre

; TMR2 modul (Timer2) bekapcsolása

bsf T2CON,7 ; fentebb egy menetben is elvégezhető szerintem

; ..TMR4.......

movlw b'01110000' ; <3:0>=utóosztó, <6:4>=előosztó, <7>=1 start, 0 stop

banksel T4CON ; előosztást 1:128-ra állítom (111) értékkel

movwf T4CON ; Megj.: Az utóosztó nincs hatássat a PWM működésre

; TMR4 modul (Timer4) bekapcsolása

bsf T4CON,7 ; fentebb egy menetben is elvégezhető szerintem

; ..TMR6................

movlw b'01110000' ; <3:0>=utóosztó, <6:4>=előosztó, <7>=1 start, 0 stop

banksel T6CON ; előosztást 1:128-ra állítom (111) értékkel

movwf T6CON ; Megj.: Az utóosztó nincs hatássat a PWM működésre

; TMR6 modul (Timer6) bekapcsolása

bsf T6CON,7 ; fentebb egy menetben is elvégezhető szerintem

; PWMx modulok bekapcsolása és kimenet polaritásának megadása

; PWMxCON<4>=0 normál polaritású a kimenet, 1-nél pedig fordított (x=5,6,7,8)

; PWMxCON<7>=0 PWMx(1-4) modul kikapcsolva, 1-nél bekapcsolva (x=5,6,7,8)

;...PWM1..........

movlw b'10000000' ; K:356

banksel PWM5CON

movwf PWM5CON

;...PWM2..........

movlw b'10000000' ; K:356

banksel PWM6CON

movwf PWM6CON

;...PWM3..........

movlw b'10000000' ; K:356

banksel PWM7CON

movwf PWM7CON

;...PWM4..........

movlw b'10000000' ; K:356

banksel PWM8CON

movwf PWM8CON

; A kimenet (IC láb) engedélyezése kimentnek (PWM kimenet)

banksel TRISC

bcf TRISA,0 ; PWM1 kimenetet -> PWM5 jel bekapcsolása

bcf TRISA,1 ; PWM2 kimenetet -> PWM6 jel bekapcsolása

bcf TRISA,2 ; PWM3 kimenetet -> PWM7 jel bekapcsolása

bcf TRISA,3 ; PWM4 kimenetet -> PWM8 jel bekapcsolása

goto konfig_

;........PWMx_PWMx..............................................................

END